VI MẠCH NHỚ:

Là vi mạch có khả năng lưu trữ dữ liệu. Về mặt điện tích thì chúng được xem như nhiều ô nhớ mà ta có thể đặt vào một giá trị điện áp là High hoặc Low. Và giá trị này sẽ được lưu trữ theo thời gian tùy theo từng loại. Có 2 loại mạch nhớ cơ bản là ROM và RAM.

III.1. Ram ( Random Access Memory):

Là bộ nhớ có thể truy xuất và ghi vào. Nói cách khác RAM là bộ nhớ thay đổi, nghĩa là nó sẽ mất dữ liệu khi bị mất nguồn nuôi.

Có 2 loại RAM sau:

III.1.1. SRAM ( Static RAM):

Được gọi là RAM tĩnh, là dạng RAM hoạt động theo nguyên tắc của Flip – Flop D. dữ liệu ghi vào được tồn trữ theo thời gian.

III.1.2. DRAM ( Dynamic RAM):

Được gọi là RAM động. Là dạng RAM hoạt động như tụ điện, do đó dữ liệu có thể bị mất sau khi ngắt điện. Vì thế đối với DRAM để đảm bảo không mất dữ liệu thì ta phải làm tươi RAM sau một khoảng thời gian ấn định.

III.2. ROM (Real Only Memory):

Là bộ nhớ chỉ có thể đọc được dữ liệu được ghi trước từ nó. Nhưng cũng có một số loại ROM ta có thể ghi vào nó với một số điều kiện đặc biệt.

ROM | |

Có thể bạn quan tâm!

-

Thiết kế và thi công Card ghi - đọc EPROM - 1

Thiết kế và thi công Card ghi - đọc EPROM - 1 -

Thiết kế và thi công Card ghi - đọc EPROM - 2

Thiết kế và thi công Card ghi - đọc EPROM - 2 -

Thiết kế và thi công Card ghi - đọc EPROM - 4

Thiết kế và thi công Card ghi - đọc EPROM - 4 -

Thiết kế và thi công Card ghi - đọc EPROM - 5

Thiết kế và thi công Card ghi - đọc EPROM - 5 -

Thiết kế và thi công Card ghi - đọc EPROM - 6

Thiết kế và thi công Card ghi - đọc EPROM - 6

Xem toàn bộ 80 trang tài liệu này.

D0

A3 A2

Andress Bus A1

A0

Control Input

Data bus

D7

sau:

Hình 1: Sơ đồ logic ROM được đơn giản hóa.

Tùy theo công nghệ chế tạo và cách thức ghi dữ liệu mà ta có các loại ROM

III.2.1. PROM (Programmable ROM ):

Là loại chỉ ghi được dữ liệu một lần và không đổi được nữa. Người sử dụng có thể tự lập trình trên PROM. Thường gọi là ROM cầu chì, có giá thành thấp, được sử dụng trong các ứng dụng quy mô nhỏ.

III.2.2. MROM (Mask – Programmed ROM):

Là loại ROM chỉ sản xuất theo đơn đặt hàng vì chỉ được lập trình một lần duy nhất và chương trình được cài sẵn trong quá trình chế tạo của nhà sản xuất.

III.2.3. EPROM (Erasable ROM):

Là loại ROM lập trình được nhiều lần. Mỗi lần lập trình sai có thể lập trình lại bằng cách xóa đi trước khi thực hiện chương trình mới.

Xóa EPROM bằng cách chiếu tia cực tím vào cửa sổ trên thân EPROM. Khi EPROM được xóa sạch có nghĩa là toàn bộ tế bào nhớ đều ở mức 1.

EPROM được ký hiệu 27xxxx.

III.2.4. EEROM (Electrically EPROM ):

EPROM có 2 nhược điểm sau:

Muốn thay đổi chương trình khác phải đem đi xóa và lập trình lại, việc này rất tốn thời gian.

Khi ta muốn thay đổi nội dung của một bit tại một địa chỉ nào đó thì phải xóa toàn bộ EPROM.

Do đó EEPROM đã ra đời để cải tiến EPROM.

EEPROM có thể xóa bằng điện. Và khi xóa có thể xóa toàn bộ hay từng từ (Word) trong ma trận nhớ.

Ký hiệu EEPROM: 28xxx.

Điện áp lập trình là 5v vì bên trong có bộ chuyển đổi DC sang DC (từ 5v÷21v).

VI MẠCH VI XỬ LÝ:

Vi xử lý là vi mạch lớn hoặc cực lớn (LSI hoặc VLSI ) có chức făng tương tự đơn vị xử lý trung tâm ( CPU: Center Processer Unit ) của máy tính thông thường nhưng mức độ thấp hơn về tốc độ cũng như về khả năng xử lý và xuất dữ liệu.

Một vi xử lý có thể thực hiện vài trăm lệnh đến hàng ngàn lệnh. Do đó nó có khả năng thực hiện được rất nhiều việc khác nhau tùy theo yêu cầu của người sử dụng.

Tính ưu việt của vi xử lý trong kỹ thuật điều khiển và đo lường ngày càng được khẳng định do tính mềm dẻo của phần mềm. Mặc dù nó phức tạp trong hoạt động thiết kế, nhưng tính kinh tế là một ưu điểm và kích thước nhỏ.

Thông thường 1 hệ vi xử lý gồm có 2 phần chính:

Phần cứng.

Phần mềm.

Phần cứng bao gồm 3 phần chủ yếu: đơn vị xử lý trung tâm (CPU), khối nhớ, khối vào ra. Ngoài ra còn có các đường dẫn tín hiệu, bộ dao động …

Phần mềm: là các chương trình do người sử dụng viết để điều khiển theo yêu cầu của mình.

Một số vi xử lý thông dụng hiện nay là Z80, 6800, 8085, 8031… Càng về sau thì các hệ vi xử lý càng tiến bộ về khả năng xử lý dữ liệu và tốc độ xử lý…

Sơ đồ cấu trúc 1 bộ vi xử lý:

![]()

CPU | |

ROM RAM I/O |

Addess Bus

OUT IN

![]()

Data Bus Control Bus

CHƯƠNG II: GIỚI THIỆU KIT PROFI – 5E

GIỚI THIỆU VỀ EPROM 2764

I.1. GIỚI THIỆU:

EPROM 2764 do hãng Intel sản xuất có các đặc điểm.

Nguồn cung cấp Vcc = 5v.

Dung lượng: 8k x 8 bit ( gồm 65.536 bit).

Thời gian tối đa để lập trình chọn IC 2764 là 420s. Thời gian truy xuất tối đa:

Chế độ bình thường là 280 ns.

Chế độ nhanh là 200ns.

Xung lập trình đơn. Công suất tiêu tán thấp.

Ở chế độ hoạt động: dòng tối đa 150mA

Ở trạng thái chờ: dòng tối đa 35mA. Hoạt động dựa trên các thông số của họ TTL. Ngõ ra 3 trạng thái.

Lập trình bằng điện và xóa bằng tia cực tím.

I.1.1. SƠ ĐỒ CHÂN CỦA EPROM 2764:

Trong đó:

A0 đến A12 bus địa chỉ (ngõ vào). D0 đến D7 bus dữ liệu (ngõ ra).

OE: điều khiển cho phép ngõ ra (ngõ vào). CE: điều khiển chọn chip (ngõ vào).

Vpp: điện áp lập trình.

PGM: xung lập trình với độ rộng cần thiết.

I.1.2. BẢNG TRẠNG THÁI HOẠT ĐỘNG EPROM 2764:

CE (20) | OE (22) | PGM (27) | VPP (1) | VCC (28) | OUTPUT (11-13,15-19) | |

Đọc | VIL | VIL | VIH | VCC | VCC | Ra |

Chờ | VIH | X | X | VCC | VCC | Z cao |

Nạp C/T | VIL | X | VIL | VPP | VCC | Vào |

Kiểm C/T | VIL | VIL | VIH | VPP | VCC | Ra |

VIH | X | X | VPP | VCC | Z cao |

Cấm nạp C/T

10

9

8

7

6

5

4

3

25

24

21

23

2

20

22

27

1

2

A3 A4 A5 A6 A7 A8 A9 A10 A11 A12

CEOE PGM VPP

A0 A1 A

00

01

02

03

04

05

06

07

11

12

13

15

16

17

18

19

2764

Trong đó các điện áp:

VIH tương ứng với mức logic 1 của TTL. VIL tương ứng với mức logic 0 của TTL. X: là trạng thái không quan tâm.

I.1.3. SÔ ÑOÀ KHOÁI EPROM 2764:

D0ữD7

OE CE/PGM

A0ữA12

Đệm ngõ ra | ||

Giải mã Y | Mạch của Y (Y gating) | |

Giải mã X | Ma trận nhớ 65.536 bit |

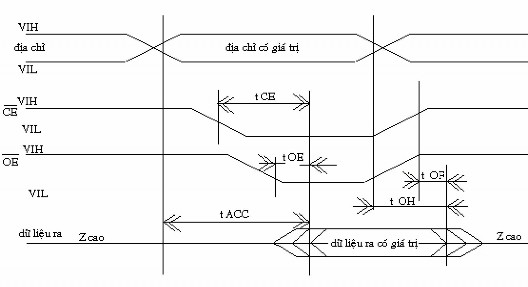

I.2. CHẾ ĐỘ ĐỌC:

Giản đồ xung chu kỳ đọc:

Khi các chân CE, OE ở mức logic 0 và Vppở +5v thì chế độ đọc được xác lập.

Dữ liệu chỉ xuất ra trong một khoảng thời gian tACC, tOE.

I.3. CHẾ ĐỘ CHỜ:

Từ bảng trạng thái, khi CE ở mức logic 1, Vppở mức +5v thì chế độ chờ được thiết lập. Ở chế độ này làm giảm công suất tiêu thụ còn 75%. Dòng điện tiêu thụ tối đa 35 mA. Các ngõ ra ở 3 trạng thái (Hi – Z ), độc lập với ngõ vào CE.

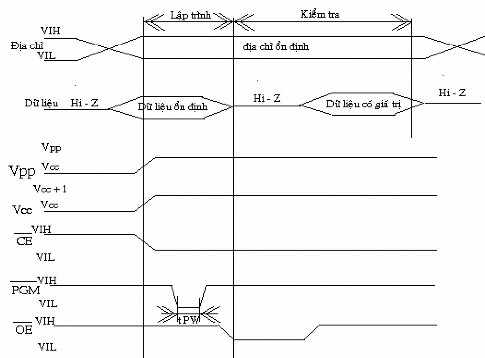

I.4. CHẾ ĐỘ LẬP TRÌNH:

Chế độ lập trình sẽ được hoàn hảo khi EPROM đã được xóa sạch. Khi đó, các bit của EPROM đều ở trạng thái logic 1. Việc lập trình được tiến hành từ địa chỉ thấp nhất đến địa chỉ cao hơn và nó sẽ kết thúc khi ta hết dữ liệu đưa vào mà không đòi hỏi là phải chiếm hết các ô nhớ của EPROM.

Để lập trình EPROM 2764 ta cần thực hiện các bước cơ bản sau: Đưa địa chỉ vào bus địa chỉ của EPROM để chọn ô nhớ lập trình.

Đưa dữ liệu cần nạp vào bus dữ liệu của EPROM. Mỗi lần dữ liệu vào thì ô nhớ tự động tăng lên 1 đơn vị.

Điện áp cần nạp EPROM 2764: Vpp =+21v hoặc =+12,5v Chân CE được nối xuống mass (mức logic 0).

Khi công việc trên đã hoàn tất nghĩa là địa chỉ và dữ liệu đã ổn định thì xung lập trình được đưa vào chân PGM.

Giản đồ xung lập trình:

Khi lập trình, người lập trình có thể thâm nhập bất kỳ ô nhớ nào vào bất kỳ lúc nào. Việc chọn địa chỉ có khoảng cách liên tục hay ngẩu nhiên.

I.5. CHẾ ĐỘ CẤM LẬP TRÌNH:

Chế độ này sẽ thực thi khi người viết chương trình điều khiển chân CE lên mức logic 1. Lúc này các ngõ ra ở tổng trở cao. Chế độ cấm lập trình nói chung và chân CE nói riêng được xem như là một công tắc chọn lựa khi mà ta lập trình song song nhiều EPROM 2764 cùng một lúc.

I.6. CHẾ ĐỘ KIỂM TRA LẬP TRÌNH:

Khi ta chuyển sang chế độ này với mục đích là kiểm tra những dữ liệu vừa nhập và xem có sai sót không. Khi kiểm tra các chân CE, OE ở mức logic 0, Vpp=

+21v.

GIỚI THIỆU VI XỬ LÝ 8085:

Vi xử lý 8085 do hãng Intel sản xuất. Đó là vi xử lý 8 bit, các vi xử lý 8 bit là sự cải tiến của các vi pử lý 4 bit ra đời vào đầu thập niên 70. Có nhiều hãng sản xuất vi xử lý 8 bit như: Intel, Motorola, Zilog… Việc chọn vi xử lý 8085 làm kit có những ưu việt của nó.

II.1. ĐẶC TÍNH ĐIỆN:

Nguồn cung cấp: 5v ±10%, Imax = 170 mA.

Tần số xung đồng hồ: 5MHz. Mạch tích xung đồng hồ được tích hợp có thể sử dụng thạch anh, mạch RC, LC bên ngoài.

Đơn vị điều khiển được tích hợp.

Có 4 vector ngắt, trong đó có một dành cho nhu cầu ngắt không ngăn được (Non

– Maskable). Và một tương thích với 8080A. Cổng vào/ra nối tiếp.

Tính nhị phân, thập phân và thập lục phân (tính 16 bit). Khả năng định địa chỉ trực tiếp 64 Kbyte.

Phần mềm tương thích 100% với Z80.

II.2. CẤU TRÚC PHẦN CỨNG 8085:

Chân | Ký hiệu | In/Out 3 state | Ý nghĩa |

1,2 | X1, X2 | I | X1, X2là 2 ngõ vào của mạch dao động. Tần số ngõ vào được chia bơĩi 2 mạch chia bên trong. Tần số làm việc phụ thuộc vào loại vi xử lý . Đối với 8085A là 6 MHz. Đối với 8085A1 là 12MHz. Đối với 8085A2 là 10MHz. |

3 | Reset out | O | Cho biết CPU đang reset. Tín hiệu này có thể dùng để reset các thành phần khác trong mạch. |

4 | SOD | O | Serial output. Ngõ ra dữ kiệu nối tiếp được xác định bởi lệnh Sim. |

5 | SID | I | Serial input ngõ vào dữ liệu nối tiếp. Nó được nạp vào bit thứ 7 của thanh ghi A khi thực hiện lệnh RIM. |

6 | TRAP | I | Trap: tín hiệu ngắt không ngăn được. Ngõ vào Trap được kích bởi cạnh lên. |

7,8,9 | RST 7,5; 6,5; 5,5 | I | Restart Interrupt Request: là các tín hiệu ngắt có thể ngăn được. |

10 | INTR | I | Interrupt: là tín hiệu ngắt thông dụng có thể che được. Lệnh được kích bằng mức. |

11 | INTA | O | Interrupt Acknowledge: tín hiệu dùng để báo cho thiết bị yêu cầu ngắt bởi tín hiệu INTR biết |

Sơ đồ chân của vi xử lý 8085 và sơ đồ logic ở hình 8. Trong đó chức năng của các chân được trình bày dưới đây:

rằng vi xử lý đã chấp nhận yêu cầu ngắt. | |||

19-12 | AD7 ữAD0 | I/O-3 | Address/databus: đường địa chỉ và dữ liệu được tích hợp chung. Ở trạng thái T1của chu kỳ máy các ngõ này đóng vai trò là ngõ ra địa chỉ. Các trạng thái còn lại của chu kỳ máy đóng vai trò đường dữ liệu. |

20 | Vss | O-3 | Ground |

28-21 | A15 ữ A18 | O-3 | Addess bus: các ngõ này dùng để xuất 8 bit địa chỉ cao. |

30 | ALE | O | Addess Latch Enable: ngõ này tạo ra 1 xung ở trạng thái T1của chu kỳ máy để xác định A15ữ A8 và AD7 ữ AD0 là các đường địa chỉ. |

31 | WR | O-3 | Write: dùng để xác định Microprocessor đang thực hiện ghi dữ liệu lên bộ nhớ hay I/O. |

32 | RD | O-3 | Read dùng để xác định Microprocessor đang thực hiện ghi dữ liệu lên bộ nhớ hay I/O. |

29, 33,34 | S0, S1 IO/M | O O-3 | Machine Cycle Status: 3 bit này cho biết trạng thái chu kỳ máy. |