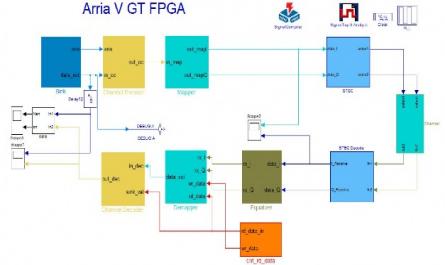

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 1

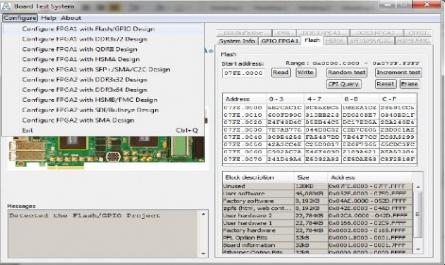

Đại Học Quốc Gia Thành Phố Hồ Chí Minh Trường Đại Học Khoa Học Tự Nhiên Khoa Điện Tử Viễn Thông Ngô Văn Hơn Thực Hiện Hệ Thống Mimo Stbc Trên Board Fpga Arria V Khóa Luận Tốt Nghiệp Cử Nhân Ngành Điện Tử Viễn Thông Chuyên Ngành: ...