Hình 2.14. Sơ đồ kết nối Anten. Các đặc tính của Anten được mô tả trong bảng sau:

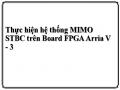

Bảng 2-1. Các đặc tính của Arria V GT.

190,240 | |

Số phần tử logic (LEs) | 504,000 |

Số RAM M10K | 24,140 |

Tổng bộ nhớ RAM | 27,046 Kb |

Đa kênh 18x18 bit | 2,312 |

PLLs | 16 |

Số bộ truyền/nhận | 36 |

Loại đóng gói | FBGA 1517 chân |

Có thể bạn quan tâm!

-

Lý Thuyết Và Công Cụ Thiết Kế

Lý Thuyết Và Công Cụ Thiết Kế -

Hệ Thống Alamouti Stbc 2X1 Tại Khe Thời Gian Thứ Nhất Tín Hiệu Nhận Được Có Dạng:

Hệ Thống Alamouti Stbc 2X1 Tại Khe Thời Gian Thứ Nhất Tín Hiệu Nhận Được Có Dạng: -

Quy Trình Thiết Kế Của Dsp Builder

Quy Trình Thiết Kế Của Dsp Builder -

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi.

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi. -

Mạch Thực Hiện Điều Chế Mimo-Stbc.

Mạch Thực Hiện Điều Chế Mimo-Stbc. -

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 9

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 9

Xem toàn bộ 87 trang tài liệu này.

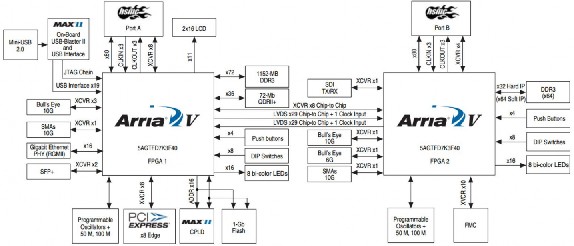

2.3.2.2 MAX II CPLD EPM2210GF324

Board này sử dụng bộ điều khiển hệ thống MAX II CPLD EPM2210 với mục

đích:

Cấu hình FPFA từ bộ nhớ Flash. Giám sát công suất tiêu thụ.

Ảo hóa giao diện JTAG cho giao diện đồ họa máy tính cơ bản (PC- based GUI).

Điều khiển thanh ghi cho xung clock.

Điều khiển thanh ghi cho quá trình điều khiển cập nhật hệ thống.

Hình 2.15. Sơ đồ khối MAX II CPLD EPM2210

2.3.3 Ứng dụng Board Test System.

2.3.3.1 Giới thiệu về Board Test System.

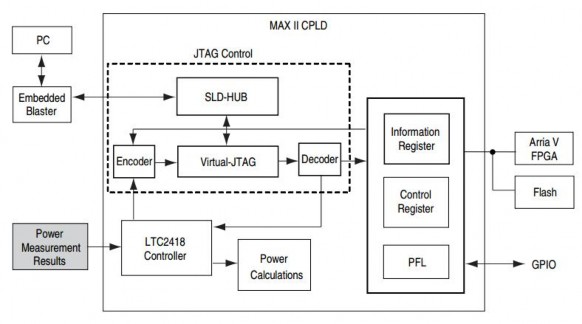

Bộ kit bao gồm một ví dụ thiết kế và một ứng dụng được gọi là Board Test System (BTS) để kiểm tra các chức năng của board Arria V. Ứng dụng này có giao diện làm rất dễ sử dụng để thay đổi các tính năng và quan sát kết quả. Ngoài ra, có thể sử dụng BTS để kiểm tra các thành phần của board, thay đổi các thông số, quan sát hiệu suất và đo công suất sử dụng của board.

Giao diện đồ họa của BTS trên máy tính giao tiếp với board thông qua bus JTAG để kiểm tra những thiết kế đang chạy trên board. Hình 2.16 là giao diện của BTS.

Hình 2.16. Giao diện Board Test System

Một số thiết kế được cung cấp để kiểm tra những đặc tính chính của board. Mỗi thiết kế sẽ có dữ liệu cho một hoặc nhiều tab trong phần ứng dụng. Nếu chọn một menu cấu hình thì một thiết kế thích hợp sẽ được tải xuống FPGA. Sau khi cấu hình FPGA thành công, một số tab sẽ xuất hiện cho phép ta thực hành một số đặc tính liên quan đến board.

2.3.3.2 Sử dụng Board Test System.

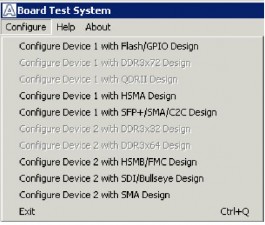

Menu cấu hình:

Sử dụng menu cấu hình để chọn những thiết kế mà ta muốn sử dụng. Mỗi thiết kế sẽ có chức năng khác nhau khi đó sẽ có một hoặc nhiều tab tương ứng sẽ xuất hiện.

Hình 2.17. Menu cấu hình Tab thông tin hệ thống:

Như hình 2.16, tab thông tin hệ thống sẽ hiển thị các thông tin sau:

Thông tin trạng thái cấu hình của board. Nội dung của thành ghi MAX II

Thông tin của các JTAG Địa chỉ MAC của board Một số lưu trữ chi tiết khác

Tab GPIO trên FPGA 1:

Tab GPIO cho phép tương tác với tất cả các thành phần nhập/xuất trên board như viết lên LCD, đọc Switch DIP, đóng tắt LED và nhận diện khi nhấn các nút nhấn.

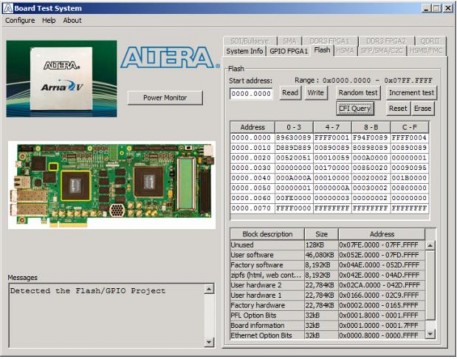

Tab Flash:

Tab flash cho phép đọc và viết tất cả bộ nhớ flash lên trên board. Hình

2.18 thể hiện rõ hơn về chức năng này.

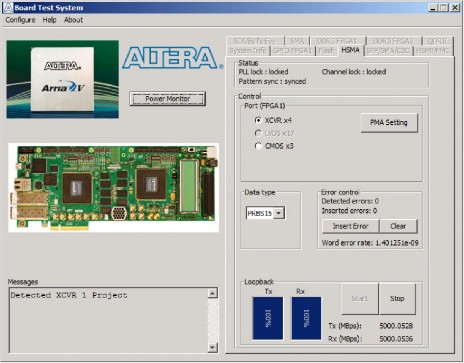

Tab HSMA:

Tab HSMA cho phép kiểm tra hồi tiếp trên bộ thu phát (XCVR) và cổng CMOS. Lưu ý là phải hồi tiếp HSMA trên cổng kết nối HSMC A thì chức năng này mới làm việc được. Hình 2.19 là giao diện làm việc của HSMA.

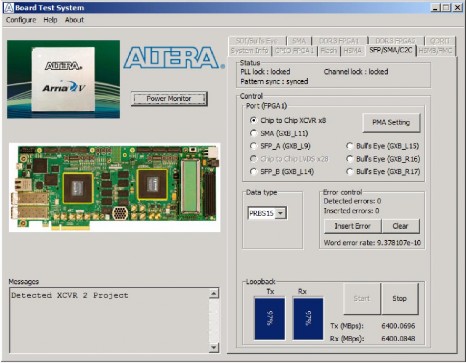

Tab SFP/SMA/C2C:

Tab SFP/SMA/C2C cho phép chạy các thiết kế kiểm tra, sử dụng giao diện kênh thu phát riêng biệt trên FPGA 1. Hình 2.20 là giao diện của tab này.

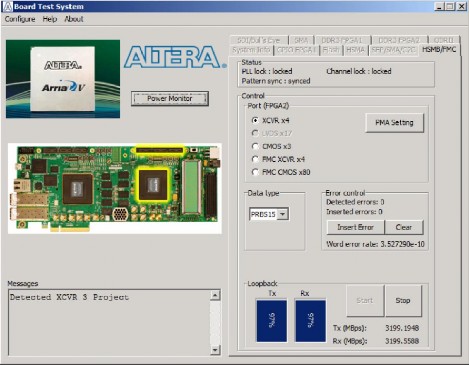

Tab HSMB/FMC:

Tab HSMB/SMC cho phép thực hiện hồi tiếp trên XCVR và cổng CMOS FPGA 2. Hình 2.21 la giao diện của tab. Chú ý là cần hồi tiếp HSMB trên cổng kết nối HSMC B thì mới kiểm tra được chức năng này.

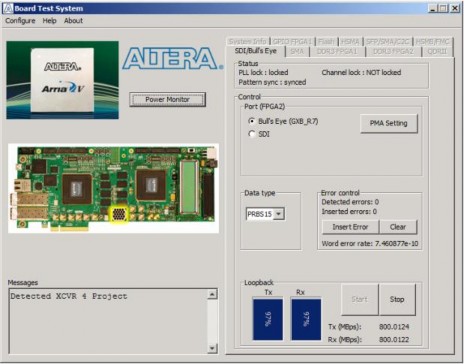

Tab SDI/Bull’s Eye:

Tab này cho phép thực hiện hồi tiếp trên cổng Bull’s Eye và SDI của FPGA 2. Tab này được thể hiện trong hình 2.22.

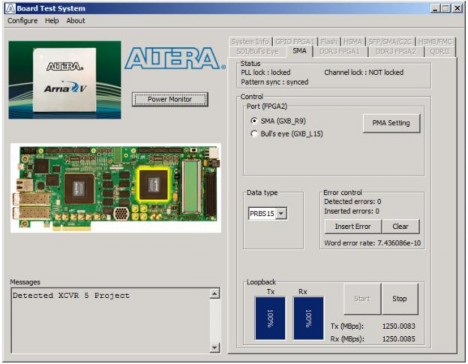

Tab SMA:

Tab SMA cho phép thực hiện hồi tiếp qua cổng SMA trên FPGA 2. Tab này có giao diện như hình 2.23.

Hình 2.18. Tab Flash

Hình 2.19. Tab HSMA

Hình 2.20. Tab SFP/SMA/C2C

Hình 2.21. Tab HSMB/FMC

Hình 2.22. Tab SDI/Bull's Eye

Hình 2.23. Tab SMA