Biên dịch và xuất ra file VHDL

Sử dụng Quartus II 64 bít phiên bản từ 11.0 trở lên, tiến hành: Bước 1: Tạo Project mới

Bước 2: Thêm thư viện là các file VHDL đã tạo ra ở trên.

Bước 3: Chọn dòng thiết bị là Arria V GT 5AGTFD7K3F40I3N. Bước 4: Biên dịch tạo ra file *.sof

Bước 5: Nạp file *.sof vào FPGA thông qua Programmer của Quartus II.

CHƯƠNG 4: KẾT QUẢ.

Có thể bạn quan tâm!

-

Sơ Đồ Kết Nối Anten. Các Đặc Tính Của Anten Được Mô Tả Trong Bảng Sau:

Sơ Đồ Kết Nối Anten. Các Đặc Tính Của Anten Được Mô Tả Trong Bảng Sau: -

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi.

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi. -

Mạch Thực Hiện Điều Chế Mimo-Stbc.

Mạch Thực Hiện Điều Chế Mimo-Stbc. -

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 10

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 10

Xem toàn bộ 87 trang tài liệu này.

Chương này trình bày các kết quả kiểm tra một số chức năng chính của board FPGA Arria V GT bằng phần mềm Board Test System đồng thời kiểm tra kết quả của hệ thống MIMO trên mô phỏng bằng khối. Các dữ liệu ở ngõ ra thường có thời gian trễ so với dữ liệu vào. Tuy từng khối cụ thể mà thời gian trễ sẽ khác nhau.

4.1 Kết quả kiểm tra board bằng phần mềm Board Test System

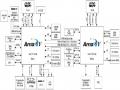

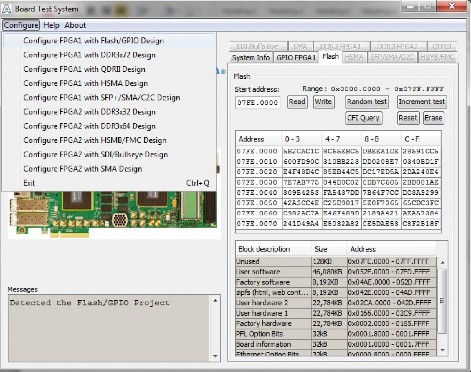

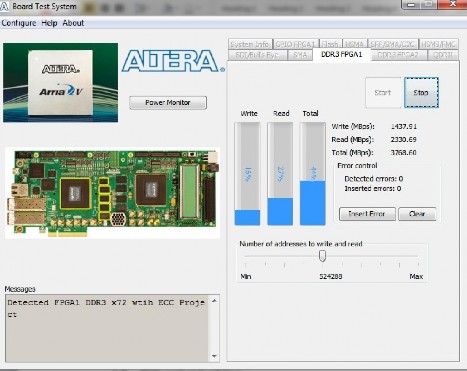

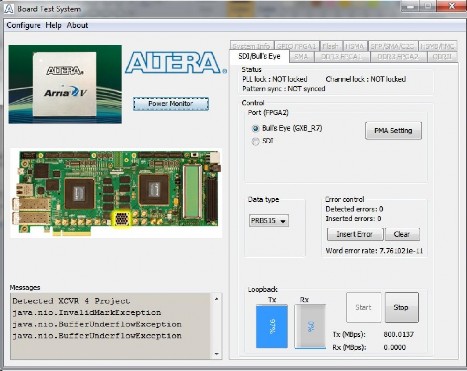

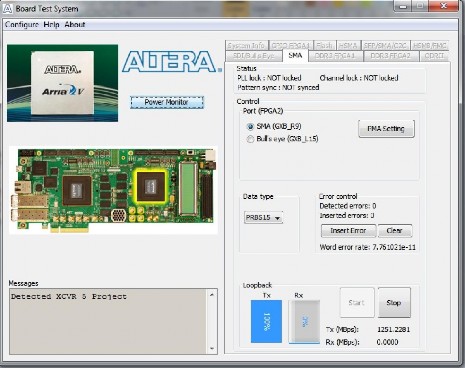

Hình 4.1Error! Reference source not found. đến Hình 4.9 cho ta thấy việc thực hiện được cấu hình và kiểm tra board Arria V GT bằng phần mềm Board Test System.

Hình 4.1. Cấu hình menu Flash/GPIO trên FPGA 1.

Hình 4.2. Kết quả cấu hình LED, LCD hiện thị, các Switch và nút nhấn.

Hình 4.3. Kết quả kiểm tra đọc, ghi bộ nhớ RAM gắn với Chip FPGA 1.

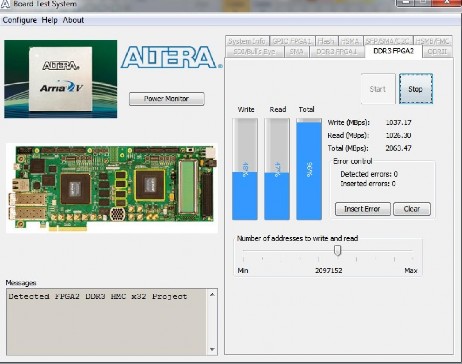

Hình 4.4. Kết quả kiểm tra đọc, ghi bộ nhớ RAM gắn với Chip FPGA 2.

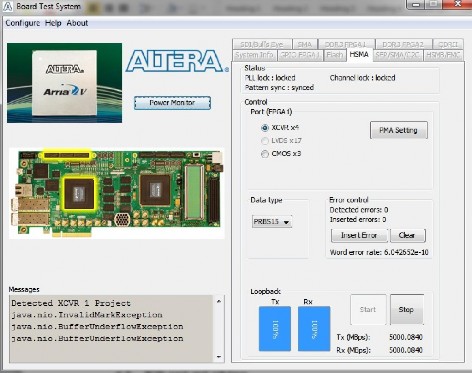

Hình 4.5. Kết quả thu phát loopback trên cổng kết nối HSMA.

Hình 4.6. Kết quả thu phát loopback trên cổng kết nối HSMB.

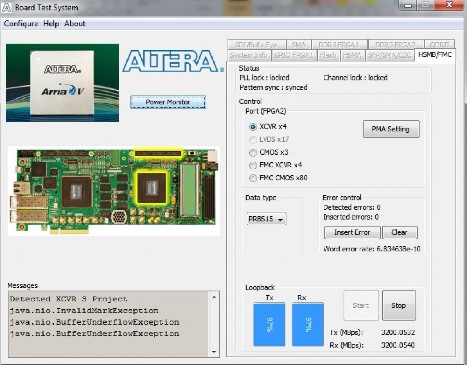

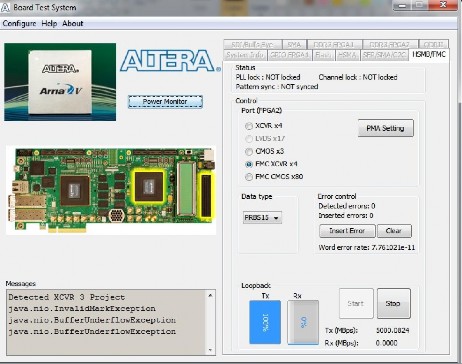

Hình 4.7. Kết quả kiểm tra phát trên cổng kết nối FMC.

Hình 4.8. Kết quả kiểm tra phát tại Bull’s Eye.

Hình 4.9. Kết quả kiểm tra thu phát qua SMA.

4.2 Kết quả đo đạt mô hình thiết kế.

4.2.1 Bộ mã hóa kênh và giải mã Viterbi

Tín hiệu qua bộ mã hóa kênh được thể hiện như hình 4.10

Hình 4.10. Tín hiệu qua mã hóa kênh

Kết quả so sánh trước và sau khi điều chế được thể hiện trong hình 4.11. Tín hiệu ở phần trên là tín hiệu qua bộ mã hóa kênh, tín hiệu ở phần ở là giải điều chế và bị chậm hơn một symbol. Kết quả phân tích cho thấy tín hiệu được giải mã trùng khớp với tín hiệu trước khi mã hóa.

Hình 4.11. Tín hiệu qua bộ mã hóa kênh và giải mã

4.2.2 Bộ điều chế giản đồ chòm sao bằng QPSK

Các tín hiệu điều chế QPSK là I và Q được thê hiện trong hình 4.12 và Hình

4.13

Hình 4.12. Tín hiệu phần thực QPSK