[sO] = (HK

s1

H)–1

y11 y12

y

HK [ ∗] ( 2.18)

21

y22∗

Có thể bạn quan tâm!

-

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 2

Thực hiện hệ thống MIMO STBC trên Board FPGA Arria V - 2 -

Lý Thuyết Và Công Cụ Thiết Kế

Lý Thuyết Và Công Cụ Thiết Kế -

Hệ Thống Alamouti Stbc 2X1 Tại Khe Thời Gian Thứ Nhất Tín Hiệu Nhận Được Có Dạng:

Hệ Thống Alamouti Stbc 2X1 Tại Khe Thời Gian Thứ Nhất Tín Hiệu Nhận Được Có Dạng: -

Sơ Đồ Kết Nối Anten. Các Đặc Tính Của Anten Được Mô Tả Trong Bảng Sau:

Sơ Đồ Kết Nối Anten. Các Đặc Tính Của Anten Được Mô Tả Trong Bảng Sau: -

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi.

Dạng Sóng Của Các Tín Hiệu Điều Khiển Của Khối Giải Mã Viterbi. -

Mạch Thực Hiện Điều Chế Mimo-Stbc.

Mạch Thực Hiện Điều Chế Mimo-Stbc.

Xem toàn bộ 87 trang tài liệu này.

Sau khi được xử lý, tín hiệu sẽ được đưa vào MLD (maximum likelihood decoder) để quyết định tính hiệu gốc. Nhờ đó, ta sẽ thu được tín hiệu ban đầu.

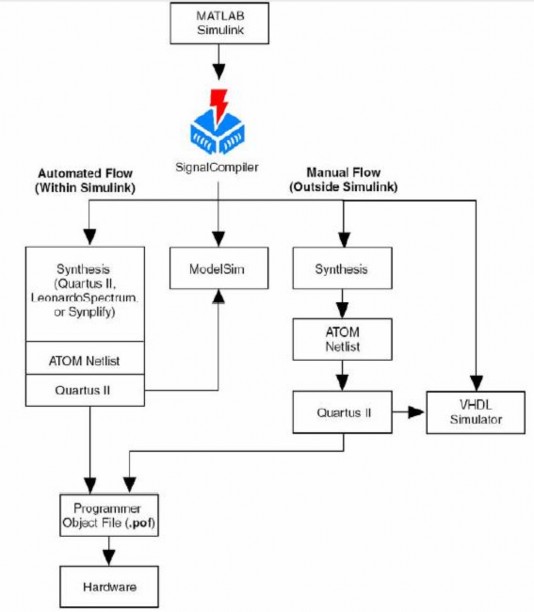

2.2 Công cụ thiết kế.

2.2.1 Phần mềm DSP Builder.

Đề tài được thiết kế bằng phần mềm DSP Builder, đây là một tiện ích do hãng Altera thiết kế nhằm hỗ trợ người sử dụng có thể thiết kế nhanh chóng các ứng dụng về xử lý tín hiệu số. DSP Builder chạy trên nền Simulink của Matlab và thừa hưởng khả năng mô phỏng của Simulink. Do đó, để sử dụng được DSP Builder thì người dùng cần biết về Matlab và Simulink trước.

DSP Buider tạo ra môi trường làm việc thân thiện để thiết kế các hệ DSP. Nhờ các khối chức năng có sẵn, việc thiết kế trở nên dễ dàng hơn. Người sử dụng có thể tạo ra những ứng dụng mong muốn và mô phỏng trên Simulink để kiểm tra kết quả.

DSP Builder cung cấp công cụ chuyển đổi thiết kế thành dạng VHDL cho phép biên dịch và tổng hợp thành các cấu hình phần cứng, giúp rút ngắn thời gian biến ý tưởng thành hiện thực.

Đặc điểm của DSP Builder là nó có các khối chứa bít và chu kỳ chính xác nên thực hiện được các chức năng về số học, lưu trữ. Chúng có thể tích hợp những chức năng phức tạp bằng cách sử dụng các MegaCore Functions trong DSP Builder model. Các Functions này tăng cường sức mạng cho DSP Builder và mở ra khả năng phát triển rộng lớn. Error! Reference source not found. trình bày các cách biên dịch để chuyển từ sơ đồ thiết kế xuống phần cứng.

Hình 2.10. Quy trình thiết kế của DSP Builder

Matlab Simulink tạo ra một model, sử dụng kết hợp các các khối DSP Builder và các khối của Simulink.

Biểu diễn mô phỏng RTL (Register Transfer Level): DSP Builder hỗ trợ mô phỏng cho phần mềm ModelSim bằng các Tcl scripts. Có thể sử dụng VHDL đã được tạo ra để mô phỏng bằng các công cụ khác.

Sử dụng các file do khối DSP Builder SignalCompiler tạo ra để tổng hợp RTL. DSP Builder hỗ trợ các Tcl scripts dùng để tổng hợp tự động bằng các chương trình phần mềm khác như: Quartus II, Synplify, Leonardo Spectrum.

Trong khóa luận này, việc biên dịch thiết kế được thực hiện bằng phần mềm Quartus II phiên bản 13.1 và phải trên nền Windows 64 bit.

2.2.2 Thư viện DSP Builder.

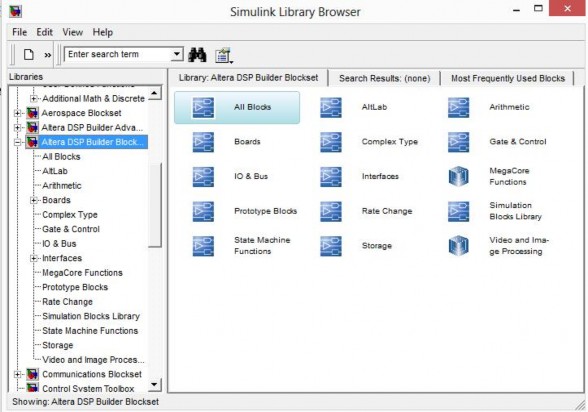

Hình 2.11. Thư viện của DSP Builder

Hình 2.11 trình bày các nhóm thư viện của DSP Builder. Tùy các phiên bản khác nhau thì DSP Builder sẽ có các thư viện thay đổi. Nhưng nhìn chung thì thư viện bao gồm các khối chức năng cơ bản như sau:

Thư viện AltLab: Đây là thư viện chứa các khối hỗ trợ thiết kết như: khối chọn loại linh kiện lập trình, khối đưa một thiết kế VHDL hoặc Verilog HDL vào trong một subsystem, khối trả về các thông tin: chu kỳ lấy mẫu, số bit tối đa cần trong quá trình mô phỏng và giá trị tối đa hoặc tối thiểu nhận khi mô phỏng. Trong thư viện có hai khối quan trọng là khối Khối SignalCompiler và Khối SignalTap II Analysis:

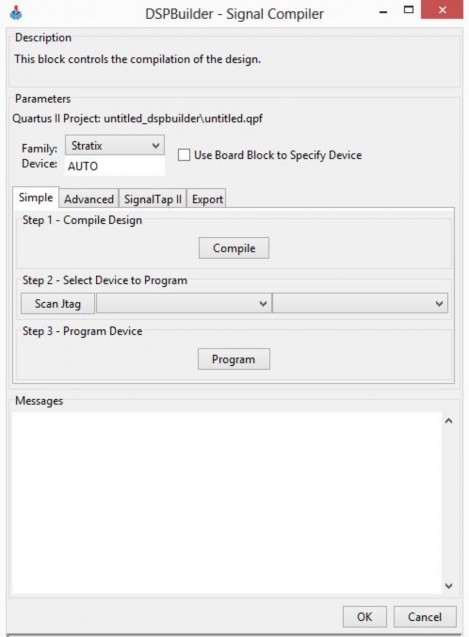

Hình 2.12. Hoạt động của khối Signal Compiler.

Khối Signal Compiler là khối quan trọng nhất trong DSP Builder. Hình 2.12 trình bày giao diện khi chạy Signal Compiler. Khối này có chức năng sau:

Chuyển đổi thiết kế Simulink sang ngôn ngữ RTL VHDL Tạo ra file kiểm tra bằng ngôn ngữ VHDL hoặc Verilog

Tạo ra Tcl scripts cho Quartus II biên dịch, hoặc cho các phần mềm khác như: Synplify, Precision RTL, LeonardoSpectrumTM và ModelSim.

Cho phép tạo ra file SignalTap II (.stp)

Tạo ra file dùng các khối định dạng trong Quartus II (.bsf)

Khối SignalTap II Analysis dùng để kiểm tra các tín hiệu bên trong linh kiện khi hệ thống đang chạy. SignalTap II Analysis có thể dùng để triggers, cấu hình bộ nhớ, và hiển thị dạng sóng. Đề tài sử dụng công cụ này để kiểm tra từng khối chức năng và quá trình xử lý dữ liệu của cả hệ thống.

Thư viện Arithmetic: Thư viện gồm các khối dùng cho phép tính số học như so sánh, vi phân, tích phân, nhân, cộng, khai căn …

Thư viện Board: Board được sử dụng trong đề tài là Board Anten. Khi muốn kết nối với phần cứng nào của board, ta chỉ cần thêm các khối trong thư viện vào mô hình thiết kế.

Thư viện Complex Type: Thư viện cung cấp các hàm liên quan đến số phức như: cộng trừ số phức, tính biên độ, pha…

Thư viện Gate and Control: Đây là thư viện cung cấp các khối về điều khiển đường đi của dữ liệu và các cổng logic như đa hợp, giải đa hợp, flip flop, cổng AND, OR, đảo…

Thư viện IO and Bus: Thư viện này cung cấp các khối vào/ra và bus như: chuyển đổi bus (ví dụ chuyển từ bus 20 bit sang bus 16 bit, bỏ đi 4 bit), tách bit, nguồn, mass, hằng số…

Thư viện Rate Change: Thư viện này cung cấp các khối để thay đổi tốc độ trong model, chủ yếu dùng khi ta muốn thiết kế chương trình có nhiều hơn 1 clock.

Khối quan trọng nhất trong thư viện này là khối PLL, và khối này chỉ có thể sử dụng được khi đặt nó ở mức cao nhất của model. Đồng thời, các khối sử dụng kết quả của PLL phải là subsystem chứ không đồng mức với PLL.

Thư viện Storage: Thư viện Lưu trữ cung cấp các khối nhớ như ROM, FIFO, LUT (look-up table: lưu trữ dữ liệu trong bảng tìm kiếm)…

Thư viện MegaCore Functions: Các MegeCore Functions là những khối có một chức năng hoàn chỉnh riêng biệt, nhưng DSP Builder không cung cấp sẵn các MegaCore Functions này. Các MegaCore Functions này có thể cài đặt thêm và thường được điều khiển rất phức tạp.

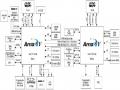

2.3 Phần cứng thực hiện.

2.3.1 Giới thiệu board Arria V GT

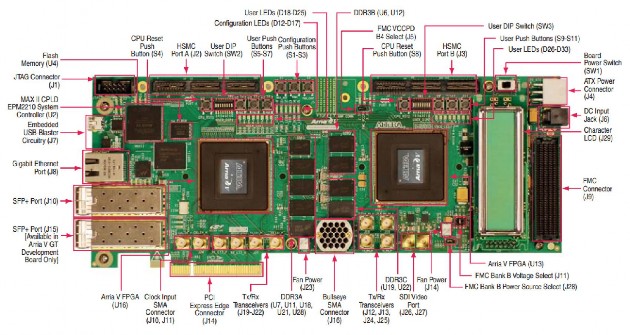

Hình 2.13. Board Anten.

Hình 2.13 là kit Development Arria V GT của hãng Altera. Kit này cung cấp một môi trường thiết kế hoàn chỉnh, bao gồm tất cả các phần cứng và phần mềm mà người sử dụng cần để phát triển tất cả những thiết kế FPGA và tiến hành kiểm tra chúng trong môi trường hệ thống. Kit có tiêu chuẩn RoHS và bao gồm các đặc điểm như sau:

Hai FPGA cho thiết kế ở mức hệ thống là Arria V GT: 504000 phần tử logic (LEs), đóng gói F1517, cho tốc độ truyền tải lên tới 10.3125 Gb/s.

Ba khe nhập/xuất gồm: 2 khe HSMC tốc độ cao và 1 khe FMC

SDRAM DDR3 với bộ nhớ 2Gb, QDR II+ với bộ nhớ 4.5Mb và bộ nhớ flash 1Gb.

Hai kết nối SFP+

Kết nối SMAs và Samtec Bull’s Eye tốc độ cao. Có thể đo công suất riêng biệt trên mỗi chip.

2.3.2 Các thành phần trên board Arria V GT.

2.3.2.1 Thiết bị Anten 5AGTFD7K3F40I3N

Trên board có 2 thiết bị quan trọng là FPGA1 và FPGA 2 họ Arria V GT với 1517 chân FineLine BGA

504000 phần tử logic (LEs)

190240 mô đun đáp ứng logic (ALMs) Bộ nhớ M10K là 24140 Kb

Bộ nhớ MLAB là 2906 Kb 36 bộ thu phát

16 vòng lặp khóa pha (PLLs) 2312 kênh 18x18.

Điện thế nội 1.15 V

FPGA 1 kết nối với các thành phần sau: Các port giao tiếp:

Một kết nối PCI Express 8 cạnh. Một kết nối USB 2.0

Cầu nối C2C với 29 ngõ vào LVDS, 29 ngõ ra LVDS và 8 kênh truyền nhận.

Hai kênh SFP+

Một kênh truyền nhận SMA 10 Gb/s

Ba kênh truyền nhận Bull’s Eye 10 Gb/s Bộ nhớ:

DDR3 SDRAM 1152 Mb với bus dữ liệu 72 bit. QDRII + SRAM 72Mb.

Flash đồng bộ với bus dữ liệu 16 bít.

Nhập/xuất:

LED và LCD:

Tám LED 2 màu xanh và đỏ. LCD hai dòng chữ.

Ba LED báo hiệu chọn cấu hình Một LED báo hiệu cấu hình xong.

Hai LED báo hiệu HSMC truyền/nhận. Ba LED báo hiệu cho PCI Express Năm LED báo hiệu Ethernet.

Nút nhấn:

Một nút nhấn reset CPU.

Một nút nhấn điều khiển cấu hình cho MAX II

Một nút nhấn để tải hình ảnh vào FPGA từ bộ nhớ flash. Một nút nhấn chọn hình ảnh để tải từ bộ nhớ flash.

Ba nút nhấn sử dụng chung. Tám switch điều khiển.

Sơ đồ kết nối của Arria V GT với các thành phần trên board như sau: