b. n+1

c. n-1

d. 0 đến n

Câu 28:

Trong TDM không đồng bộ, nếu có n nguồn tín hiệu, mỗi frame có m slot, m thường ra sao so với n:

a. Nhỏ hơn

b. nhiều hơn

c. bằng

d. nhỏ hơn 1

Câu 29:

Có thể bạn quan tâm!

-

Đường Truyền Vô Tuyến Tần Số Thấp

Đường Truyền Vô Tuyến Tần Số Thấp -

Kỹ Thuật Ghép Kênh Phân Chia Theo Tần Số Fdm

Kỹ Thuật Ghép Kênh Phân Chia Theo Tần Số Fdm -

Kỹ Thuật Ghép Kênh Phân Chia Theo Mã Cdm

Kỹ Thuật Ghép Kênh Phân Chia Theo Mã Cdm -

Truyền Đồng Bộ Thiên Hướng Ký Tự

Truyền Đồng Bộ Thiên Hướng Ký Tự -

Truyền số liệu - 15

Truyền số liệu - 15 -

Điều Khiển Liên Kết Dữ Liệu

Điều Khiển Liên Kết Dữ Liệu

Xem toàn bộ 210 trang tài liệu này.

Trong TDM không đồng bộ, tốc độ truyền của đường ghép kênh thường ra sao so với tốc độ truyền của nguồn tín hiệu:

a. Thấp hơn

b. cao hơn

c. bằng

d. nhỏ hơn 1

Câu 30:

Dạng ghép kênh nào có nhiều đường truyền

a. FDM

b. TDM không đồng bộ

c. TDM đồng bộ

d. ghép kênh nghịch

CHƯƠNG 4: TRUYỀN DẪN ĐỒNG BỘ VÀ BẤT ĐỒNG BỘ

4.1. Truyền dẫn bất đồng bộ

4.1.1. Khái quát

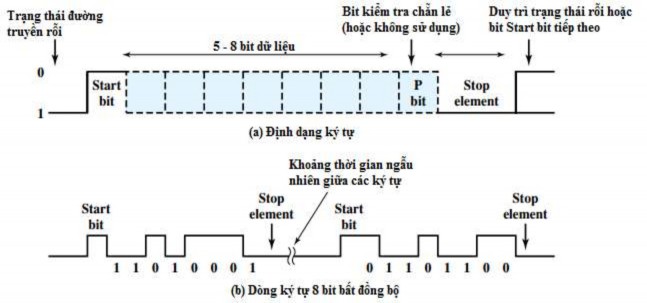

Trong kỹ thuật truyền dẫn, có hai phương pháp phổ biến để đạt được sự đồng bộ như mong muốn. Phương pháp thứ nhất, với cái tên có thể dễ gây nhầm lẫn, đó là kỹ thuật truyền dẫn bất đồng bộ. Mục đích của phương pháp này là tránh vấn đề định thời bằng cách gửi đi dòng bit không quá dài, không bị gián đoạn. Thay vào đó, dữ liệu sẽ được truyền đi dưới dạng từng ký tự với chiều dài từ 5 đến 8 bit và khoảng cách các ký tự là ngẫu nhiên. Sự đồng bộ hay định thời chỉ cần duy trì trong mỗi ký tự. Phía máy thu sẽ đồng bộ lại tại điểm bắt đầu của một ký tự mới.

Mỗi ký tự có thể gồm 5 bit đối với mã Baudot, 7 bit nếu là mã ASCII (American Standard Code for Information Interchange) và 8 bit nếu là mã EBCDIC (Extended Binary-Coded Decimal Information Code, mã BCD mở rộng).

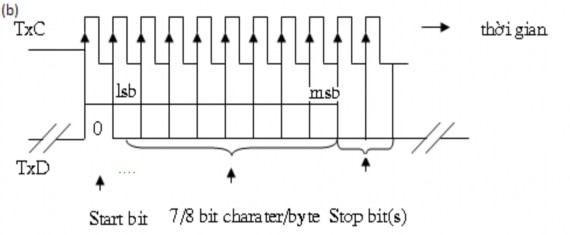

Hình 4.1 minh họa cho chế độ truyền dẫn bất đồng bộ. Khi không có dữ liệu truyền giữa máy thu và máy phát thì trạng thái đường truyền là rỗi. Định nghĩa trạng thái rỗi của đường truyền tương đương với tín hiệu bit 1. Điểm bắt đầu của mỗi ký tự được báo hiệu bởi start bit với giá trị nhị phân là 0 (có thể là mức điện áp hoặc dòng điện), tiếp đến là từ 5 đến 8 bit mang thông tin của ký tự, ta gọi là các bit dữ liệu. Trong nhiều trường hợp, các bit dữ liệu được theo sau bởi bit kiểm tra chẵn lẻ. Bit này thiết lập bởi máy phát dựa vào tổng số bit 1 trong ký tự, bao gồm cả bit kiểm tra, là chẵn (kiểm tra chẵn) hay là lẻ (kiểm tra lẻ), phụ thuộc vào sự thuận lợi khi sử dụng. Máy thu sử dụng bit này để phát hiện lỗi mà sẽ được trình bày trong chương sau. Phần tử cuối cùng là các stop bit, với giá trị nhị phân là 1. Chiều dài nhỏ nhất cho phần tử stop có thể bằng 1, 1.5 hoặc 2 lần thời gian của một bit thông thường. Không quy định chiều dài tối đa cho phần tử stop. Bởi vì phần tử stop giống với trạng thái đường truyền rỗi nên máy phát sẽ tiếp tục truyền đi phần từ stop cho đến khi nó sẵn sàng gửi một ký tự tiếp theo.

Các yêu cầu định thời cho kỹ thuật này không khắt khe. Ví dụ, các ký tự IRA cơ bản là được gửi đi một khối gồm 8 bit, bao gồm cả bit kiểm tra chẵn lẻ. Nếu máy thu nhanh hoặc chậm hơn máy phát 5% thì việc lấy mẫu của bit thứ 8 trong ký tự sẽ bị dời đi 45%, và vẫn sẽ được lấy mẫu đúng.

Hình 4.1. Truyền dẫn bất đồng bộ

Ví dụ 4.1:

Giả sử tốc độ truyền dữ liệu của máy phát là 10 Kbps. Máy thu nhanh hơn máy phát 6%. Hãy cho biết trong trường hợp này có xảy ra lỗi thu không?

Giải:

Vì tốc độ truyền dữ liệu của máy phát là 10 Kbps, nên thời gian của một bit là

0,1µs.

Máy thu nhanh hơn máy phát 6%, tương đương với 6µs/ thời gian bit. Do đó,

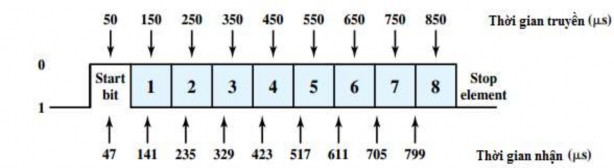

máy thu lấy mẫu các ký tự nhận được là cứ 94 µs (tính theo đồng hồ máy phát). Và như vậy mẫu cuối cùng sẽ bị lỗi. Hình 4.2 chỉ ra ảnh hưởng của một lỗi định thời đủ lớn để gây ra lỗi khi thực hiện việc nhận dữ liệu.

Hình 4.2. Ảnh hưởng của lỗi định thời

Chú ý:

- Dữ liệu của một ký tự truyền theo thứ tự thời gian là bit có trọng số thấp nhất (LSB) truyền trước và bit có trọng số cao nhất (MSB) truyền sau.

Kỹ thuật truyền dẫn bất đồng bộ thường được ứng dụng trong các bộ phát ngẫu nhiên (keyboard) hay các bộ phát dữ liệu tốc độ thấp < 20Kbps.

Ví dụ 4.2: Người sử dụng (user) nhập ký tự từ bàn phím vào máy tính. Rò ràng, với dạng thông tin này, người sử dụng gò bàn phím theo một tốc độ không xác định vào khoảng thời gian giữ hai ký tự nhập thành công là ngẫu nhiên. Điều này có nghĩa là tín hiệu trên đường dây sẽ ở trạng thái nhàn rỗi (marking) trong một khoảng thời gian dài giữa hai ký tự. Do vậy, với dạng thông tin này buộc máy thu phải đồng bộ trở lại tại thời điểm đầu của mỗi ký tự mới đến. Để thực hiện được điều này thì trước khi truyền mỗi ký tự đều được đóng gói giữa một start bit và một hay nhiều stop bit.

Truyền dẫn bất đồng bộ được sử dụng khá rộng rãi do việc phối ghép các đầu cuối dữ liệu theo phương thức truyền này có giá tương đối rẻ. Phần lớn các máy tính các nhân dùng các interface không đồng bộ do yêu cầu về đồng bộ giữa thiết bị thu được thực hiện trên cơ sở từng ký tự. Sai lệnh do sự không chính xác về định thời giữa bên phát và bên thu bị giới hạn chỉ trong mỗi ký tự. Nói cách khác, một độ chính xác thấp giữa định thời thu và định thời phát vẫn chấp nhận được, nhờ vậy giảm giá thành các thành phần.

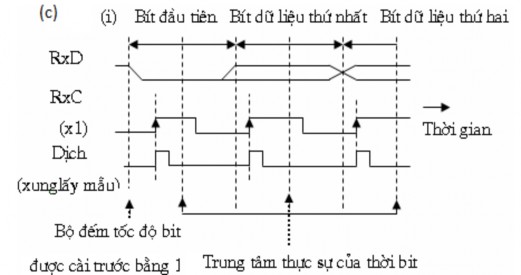

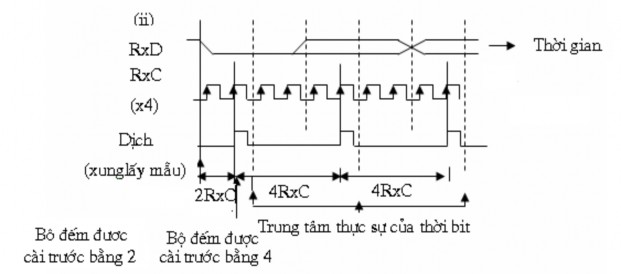

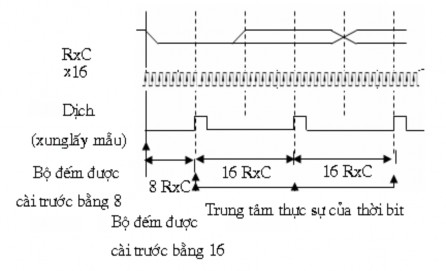

Trong truyền dẫn bất đồng bộ, đồng hồ thu không được đồng bộ với đồng hồ phát. Để xử lý thu hiệu quả, cần phải có kế hoạch dùng đồng hồ thu để lấy mẫu tín hiệu đến ngay điểm giữa thời bit của dữ liệu.

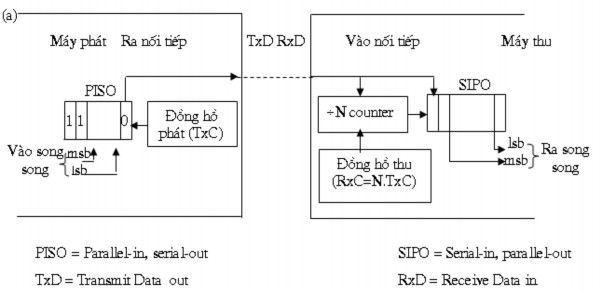

Để đạt được điều này, tín hiệu đồng hồ thu nhanh gấp N lần đồng hồ phát và mỗi bit dịch vào SIPO sau N chu kỳ xung đồng hồ. Sự chuyển trạng thái từ 1 xuống 0 là dấu hiệu của start bit có ý nghĩa bắt đầu của một ký tự và chúng được dùng để khởi động bộ đếm xung đồng hồ ở máy thu. Mỗi bit bao gồm cả start bit, được lấy mẫu tại khoảng giữa thời bit. Ngay sau khi phát hiện, start bit được lấy mẫu sau N/2 chu kỳ xung đồng hồ, được tiếp tục lấy mẫu sau mỗi N xung đồng hồ tiếp theo cho mỗi bit cho ký tự. Lược đồ tổng quát được trình bày trên hình 4.3 a; các nguyên lý định thời trên hình 4.3 b và 3 ví dụ về tỉ lệ tốc độ xung đồng hồ khác nhau trong phần 4.3 c.

Hình 4.3. Truyền bất đồng bộ: a) Nguyên lý hoạt động; b) Các nguyên tắc định thời; c) Ví dụ về tốc độ xung đồng hồ khác nhau.

Chú ý: Đồng hồ thu chạy không đồng bộ với tín hiệu đến, các vị trí tương đối của hai tín hiệu có thể ở bất kỳ vị trí nào trong một chu kỳ của xung đồng hồ thu, với N càng lớn thì vị trí lấy mẫu có khuynh hướng gần giữa thời bit. Do vậy ở chế độ truyền này tốc độ truyền không thể cao được.

4.1.2. Nguyên tắc đồng bộ bit

- Trong kỹ thuật truyền dẫn bất đồng bộ, trước khi truyền các bit dữ liệu thì máy phát gửi đi 1 start bit.

- Tại máy thu, khi chưa có dữ liệu thì đường truyền ở trạng thái rỗi, giá trị nhị phân là 1, bộ chia N chưa cho phép hoạt động → chưa có tín hiệu lấy mẫu.

- Khi phát hiện được trạng thái chuyển đổi mức điện áp (vị trí bắt đầu của start bit) thì phía thu sẽ chờ sau N/2 chu kỳ xung đồng hồ thu (vị trí giữa của start bit) để lấy mẫu. Sau đó, cứ sau mỗi N chu kỳ xung đồng hồ thì tạo ra một xung lấy mẫu, xung lấy mẫu có đặc điểm là tần số bằng tần số xung đồng hồ phía máy phát. Khi N càng lớn thì xung lấy mẫu càng tiến về điểm giữa của bit.

- Sau khi có xung lấy mẫu, tín hiệu sẽ được lấy mẫu và so sánh với mức ngưỡng tối ưu để quyết định bit đã phát là 0 hoặc 1.

- Stop bit dùng để thiết lập lại đường truyền trở về trạng thái rỗi sau khi truyền xong một ký tự. Nhờ có stop bit mà 2 ký tự liên tiếp nhau vẫn có thể thực hiện được quá trình đồng bộ bit.

Chú ý: Sự đồng bộ càng chính xác khi N càng lớn.

4.1.3. Nguyên tắc đồng bộ ký tự

Sau khi đồng bộ bit quá trình đồng bộ ký tự sẽ diễn ra như sau:

- Máy phát và máy thu được điều khiển để có cùng số bit trong mỗi chuỗi bit truyền đi (start, data, parity và stop bit) phát và thu bằng nhau.

- Sau khi nhận được start bit, phía thu sẽ thực hiện việc đồng bộ ký tự bằng cách đếm số bit đã được lập trình. Sau đó chuyển nội dung ký tự vừa thu được vào bộ đệm và chờ thu ký tự mới

- Để quy định chuẩn truyền thông (protocol), người ta thường dùng cách viết tổng hợp các thông số: tốc độ, data bit, parity bit, stop bit.

Ví dụ 4.3: 300 7 E 1 hoặc 9600 8 N 1 hoặc 1200 7 O 1 300: chỉ tốc độ, đơn vị là bps

7: chỉ số bit dữ liệu

E (event): kiểm tra parity chẵn 1: stop bit

N (none): không có chế độ kiểm tra parity O (odd): kiểm tra parity lẻ

4.1.4. Nguyên tắc đồng bộ khung (frame)

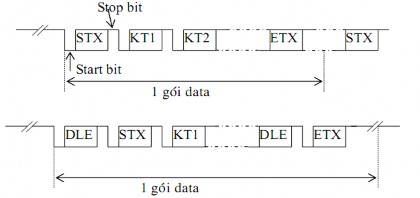

- Trong việc truyền dữ liệu, thông tin được truyền đi theo các khung. Do đó, để thu được hoàn chỉnh một khung thì phía thu phải xác định được vị trí bắt đầu và kết thúc của khung, điều này được gọi là đồng bộ khung.

- Nếu khối dữ liệu truyền là dạng in được (printable character):

Máy phát phát đi ký tự bắt đầu khung là STX (Start of Text) và phát đi ký tự kết thúc một khung là ETX (End of Text).

Máy thu dựa vào STX và ETX để thu được hoàn chỉnh nội dung một khung dữ liệu.

- Nếu khối dữ liệu truyền đi có chứa các ký tự không in được (non-printable character) ví dụ như STX hoặc ETX thì việc đồng bộ khung được thực hiện bằng cách chèn thêm ký tự DLE (Data Link Esc):

Bắt đầu khung là DLE + STX. Kết thúc khung là DLE + ETX.

- Nếu trong nội dung khối dữ liệu truyền có chứa ký tự DLE thì nó phải truyền một cặp ký tự DLE liên tiếp. Máy thu khi nhận được một cặp ký tự DLE liên tiếp trong nội dung thu thì đồng bộ thành một ký tự DLE.

Hình 4.4. Đồng bộ khung

Giả sử khi phát: “A B C” thì bên phía thu sẽ thu được: STX A B C ETX

Ví dụ 4.4:

Một khối dữ liệu được truyền qua một liên kết số liệu nối tiếp. Nếu một đồng hồ có tần số 19,2 kHz tại máy thu, hãy suy ra tỉ lệ tốc độ đồng hồ thích hợp và ước lượng độ lệch trong trường hợp xấu nhất từ trung tâm của thời bit danh định, biểu diễn theo phần trăm của thời bit cho các tốc độ truyền số liệu sau đây:

a) 1200bps

b) 2400bps

c) 9600bps

Giải:

Có thể dễ dàng suy ra từ hình 4.3(c) ở trên rằng độ lệch trong trường hợp xấu nhất là xấp xỉ một chu kỳ của xung đồng hồ. Do đó:

a) Với tốc độ 1200bps thì tỉ lệ RxC cực đại có thể là x16. Độ lệch tối đa là 6,25%.

b) Với tốc độ 2400bps thì tỉ lệ RxC cực đại có thể là x8. Độ lệch tối đa là 12,5%.

c) Với tốc độ 9600bps thì tỉ lệ RxC cực đại có thể là x2. Độ lệch tối đa là 50%.

Rò ràng trường hợp sau cùng là không thể chấp nhận được. Với đường dây chất lượng thấp, đặc biệt phải chịu trễ lớn thì ngay cả trường hợp thứ hai cũng không tin cậy. Điều này giải thích vì sao tỉ lệ x16 luôn được dùng bất cứ khi nào có thể.

Nhận xét:

Kỹ thuật truyền dẫn bất đồng bộ yêu cầu định thời đơn giản thực hiện đơn giản và chi phí thấp, tuy nhiên các bit overhead (bao gồm các bit dành cho điều khiển, kiểm tra) có thể lên đến 2, 3 bit trên mỗi ký tự. Giả sử, với một ký tự 8 bit không sử dụng bit kiểm tra chẵn lẻ, chèn thêm 1 start bit và 2 stop bit thì cứ 10 bit lại có 3 bit overhead để đồng bộ. Khi đó, hiệu suất truyền cao nhất là:

= số bit thông tin/ Tổng số bit truyền = 8/ (8+1+2) = 0,727 = 72,7 %

Trong thực tế, nếu có sử dụng bit kiểm tra chẵn lẻ (parity bit) thì giá trị này còn nhỏ hơn. Tỉ lệ các bit overhead có thể giảm đi khi ta tăng số bit cho mỗi khối dữ liệu truyền