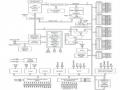

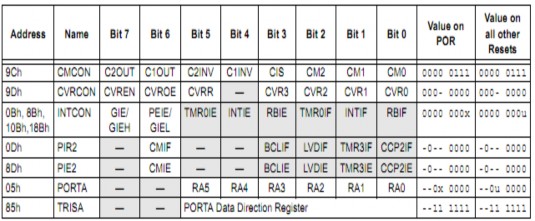

Hình 2.11 Các thanh ghi liên quan đến bộ so sánh

2.6 TRUYỀN THÔNG NỐI TIẾP EUART

EUSART (Enhanced Universal Synchronous Asynchronous Receiver Transmitter) là một bộ truyền thông nối tiếp. Nó có tất cả các bộ phát xung clock, đăng ký thay đổi và bộ đệm dữ liệu cần thiết để thực hiện một đầu vào hay đầu ra dữ liệu nối tiếp chuyển giao độc lập của thiết bị thực hiện chương trình. EUSART còn được gọi là giao diện giao tiếp nối tiếp SCI (Serial Communication Interface).

Bộ EUSART là một trong hai hình thức giao tiếp nối tiếp vào ra. EUSART có thể được cấu hình như là một hệ thống bất đồng bộ hoạt động song công mà có thể giao tiếp với các thiết bị bên ngoài như là các thiết bị đầu cuối CRT và các máy tính cá nhân nó cũng có thể được cấu hình như là một hệ thống đồng bộ hoạt động bán công mà có thể giao tiếp với các mạch tích hợp A/D hay D/A, các EEPROM nối tiếp….EUSART có thể được cấu hình để hoạt động một trong các chế độ sau:

Bất đồng bộ (song công: Asynchronous).

Đồng bộ chủ (bán công: Master mode).

Đồng bộ tớ (bán công: Slave mode).

2.6.1 Bộ EUSART hoạt động trong chế độ bất đồng bộ

Có thể bạn quan tâm!

-

Thiết kế mạch tự động cân bằng nhiệt độ và điều khiển thiết bị thông qua tin nhắn SMS - 2

Thiết kế mạch tự động cân bằng nhiệt độ và điều khiển thiết bị thông qua tin nhắn SMS - 2 -

Giới Thiệu Pic (Programmable Intelligent Computer)

Giới Thiệu Pic (Programmable Intelligent Computer) -

Nguyên Lý Hoạt Động Của Một Bộ So Sánh Đơn Giản

Nguyên Lý Hoạt Động Của Một Bộ So Sánh Đơn Giản -

Thiết Kế Mạch Tự Động Cân Bằng Nhiệt Độ Và Điều Khiển Thiết Bị Thông Qua Tin Nhắn Sms

Thiết Kế Mạch Tự Động Cân Bằng Nhiệt Độ Và Điều Khiển Thiết Bị Thông Qua Tin Nhắn Sms -

Sơ Đồ Khối Hệ Thống Điều Khiển Thiết Bị Bằng Sms

Sơ Đồ Khối Hệ Thống Điều Khiển Thiết Bị Bằng Sms -

Kết Quả Đạt Được Của Hệ Thống

Kết Quả Đạt Được Của Hệ Thống

Xem toàn bộ 80 trang tài liệu này.

Ở chế độ truyền này EUSART hoạt động theo chuẩn NRZ (None-Return-to- Zero), nghĩa là các bit truyền đi sẽ bao gồm 1 bit Start, 8 hay 9 bit dữ liệu (thông thường là 8 bit) và 1 bit Stop. Bit LSB sẽ được truyền đi trước. Các khối truyền và nhận data độc lập với nhau sẽ dùng chung tần số tương ứng với tốc độ baud cho quá trình dịch dữ liệu (tốc độ baud gấp 16 hay 64 lần tốc độ dịch dữ liệu tùy theo giá trị của bit BRGH), và để đảm bảo tính hiệu quả của dữ liệu thì hai khối truyền và nhận phải dùng chung một định dạng dữ liệu.

Bộ EUSART bất đồng bộ bao gồm các thành phần quan trọng sau:

Bộ phát tốc độ baud (BRG).

Mạch lấy mẫu.

Bộ phát bất đồng bộ.

Bộ thu bất đồng bộ.

2.6.1.1 Bộ phát bất đồng bộ EUSART

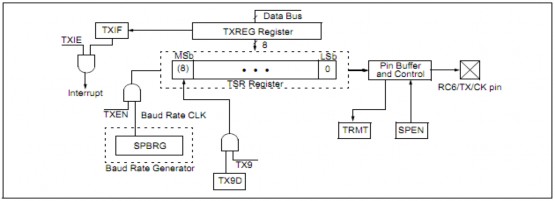

Sơ đồ khối bộ phát EUSART bất đồng bộ được chỉ ra hình vẽ 1.12. Phần chính của nó là thanh ghi dịch nối tiếp phát (TSR). Nó nhận dữ liệu từ thanh ghi đệm phát TXREG. Thanh ghi TXREG được nạp dữ liệu bởi phần mềm. Thanh ghi TXR sẽ không được nạp dữ liệu cho đến khi stop bit đã được phát đi trong lần nạp trước đó. TSR được nạp giá trị mới từ thanh ghi TXREG. Mỗi khi TXREG phát dữ liệu đến TSR. TXREG rỗng và cờ TXIF được bật. Ngắt này có thể được cho phép hoặc không cho phép bằng cách đặt hoặc xóa bit TXIE. Cờ TXIF sẽ được đặt bất chấp trạng thái của bit TXIE và không thể được xóa bởi phần mềm. Nó chỉ có thể được xóa khi dữ liệu mới được nạp vào thanh ghi TXREG. Trong khi bit TXIF chỉ ra trạng thái của thanh ghi TXREG thì bit TRMT lại chỉ ra trạng thái của thanh ghi TSR. Bit này chỉ có thể đọc, được đặt khi thanh ghi TSR rỗng.

Việc phát dữ liệu được phép bằng cách cho phép bit TXEN. Việc phát dữ liệu thực sư không xảy ra cho đến khi thanh ghi TXREG được nạp dữ liệu và bộ BRG tạo ra một clock dịch. Việc phát dữ liệu cũng có thể được bắt đầu bằng nạp thanh ghi TXREG và cho phép bit TXEN.

Để có thể phát 9 bit dữ liệu, bit TX9 được đặt và 9 bit dữ liệu được ghi đến bit TX9D. Bit thứ 9 phải được ghi trước khi ghi 8 bit dữ liệu đến TXREG.

Để thiết lập chế độ phát bất đồng bộ, các bước sau được thực hiện:

Thiết lập tốc độ Baud cho thanh ghi SPBRGH: SPBRG, nếu tốc độ baud được yêu cầu cao, đặt bit BRGH.

Set chân điều khiển RX/DT và TX/CK bằng “1”.

Cho phép port nối tiếp bất đồng bộ bằng cách xóa bit SYNC và bit SPEN.

Nếu cần phát 9 bit dữ liệu, đặt bit TX9.

Set bit điều khiển CKTXP nếu dữ liệu phát bị đảo ngược.

Cho phép phát dữ liệu bằng cách đặt bit điều khiển TXEN, có thể ngắt bit TXIF

Nếu ngắt được yêu cầu, cho phép bit TXIE. Trường hợp có sử dụng ngắt, phải bảo đảm rằng bit GIE và bit PEIE trong thanh ghi INTCON được đặt.

Nếu cần phát 9 bit dữ liệu, bit thứ 9 sẽ phụ thuộc vào bit dữ liệu TX9D.

Nhận 8 bit dữ liệu từ thanh ghi TXREG. Có thể bắt đầu truyền dữ liệu.

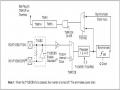

Hình 2.12 Sơ đồ khối bộ truyền dữ liệu EUSART bất đồng bộ

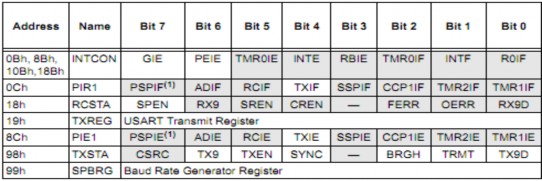

Hình 2.13 Các thanh ghi liên quan đến quá trình truyền bất đồng bộ

2.6.1.2 Bộ thu bất đồng bộ EUSART

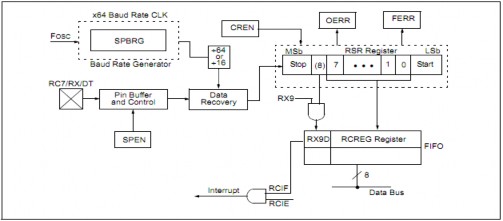

Sơ đồ khối của bộ thu được chỉ ra ở hình vẽ 1.14. Dữ liệu nhận trên chân RC7/RX/DT và dồn vào khối khôi phục dữ liệu. Khối khôi phục dữ liệu thật ra là dịch dữ liệu tốc độ cao, hoạt động nhanh gấp 16 lần tốc độ Baud. Một khi chế độ bất đồng bộ được chọn thì việc tiếp nhận được phép bằng cách đặt Bit CREN.

Trung tâm của bộ nhận là thanh ghi dịch nhận RSR. Sau khi lấy mẫu Bit Stop dữ liệu nhận trong RSR được truyền đến thanh ghi RCREG. Nếu việc truyền hoàn tất thì Bit Cờ RCIF lên 1. Ngắt thật sự cho phép hoặc không cho phép bằng cách đặt hoặc xóa Bit RCIE. Cờ RCIF chỉ là 1 Bit chỉ đọc và được xó bởi phần cứng. Nó được xóa khi thanh ghi RCREG được đọc và hoàn toàn không có dữ liệu. RCREG là 1 thanh ghi bộ đệm đôi (Bởi vì nó cho 2 Byte dữ liệu có thể truyền và nhận đồng thời đến RCREG FIFO và Byte thứ 3 bắt đầu được dịch chuyển đến thanh ghi RSR). Khi phát hiện ra Bit Stop của Byte thừ 3 này. Nếu thanh ghi RCREG vẫn còn đầy thì Bit bào lỗi tràn OERR, sẽ lên 1. Những dữ liệu trong RSR sẽ mất đi. Và thanh ghi RCREG có thể

được đọc 2 lần để lấy lại 2 Byte trong FIFO. Bit báo tràn OERR phải được xóa trong phần mềm.

Để thiết lập chế độ thu bất đồng bộ, các bước sau được yêu cầu :

1. Khởi tạo thanh ghi SPBRGH: SPBRG, BRGH và BRG16 bit cho việc chọn sai số tốc độ Baud.

2. Set chân điều khiển RX/DT và TX/CK bằng “1”.

3. Cho phép nhận qua Port nối tiếp bất đồng bộ bằng cách xóa Bit SYNC và cho Bit SPEN lên 1.

4. Nếu ngắt xảy ra thì set Bit RCIE và nếu sử dụng ngắt thì set bit GIE và PEIE của thanh ghi INTCON.

5. Nếu nhận 9-Bit dữ liệu thì set Bit RX9.

6. Set bit CKTXP nếu dữ liệu nhận bị đảo ngược.

7. Cho phép nhận dữ liệu bằng cách set Bit CREN.

8. Sau khi dữ liệu được nhận, Bit cờ ngắt RCIF sẽ được set và cờ ngắt được kích hoạt (nếu bit RCIE được set).

9. Đọc nội dung thanh ghi RCSTA để nhận bit dữ liệu thứ 9 và xác định các lỗi xảy trong quá trình thu dữ liệu.

10. Nhận 8 bit dữ liệu thu được bằng cách đọc nội dung thanh ghi RCREG.

11. Nếu xuất hiện lỗi trong quá trình nhận thì xóa lỗi bằng cách xóa Bit CREN.

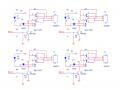

Hình 2.14 Sơ đồ khối bộ nhận dữ liệu EUSART bất đồng bộ

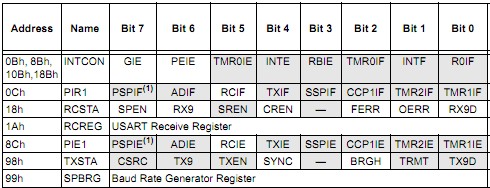

Hình 2.15 Các thanh ghi liên quan đến quá trình nhận dữ liệu bất đồng bộ

2.6.1.3 Độ chính xác của xung clock với hoạt động không đồng bộ

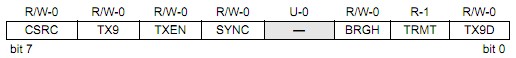

Hình 2.16 Cấu tạo thanh ghi TXSTA

Bit 7 CSRC: bit chọn nguồn xung. Chế độ bất đồng bộ: không cần thiết Chế độ đồng bộ:

+ 1 = chế độ chủ (phát xung dao động nội từ BRG).

+ 0 = chế độ tớ (xung dao dộng ngoại).

Bit 6 TX9: bit cho phép truyền 9 bit.

+ 1 = chọn chế độ truyền 9 bit.

+ 1 = chọn chế độ truyền 8 bit.

Bit 5 TXEN: bit cho phép truyền.

+ 1 = cho phép truyền.

+ 0 = không cho phép truyền.

Bit 4 SYNC: bit chọn chế độ USART.

+ 1 = chế độ đồng bộ.

+ 0 = chế độ bất đồng bộ.

Bit 3 SEND8: gửi bit ký tự bị mất. Chế độ bất đồng bộ:

+ 1 = truyền ký tự bị mất

+ 0 = quá trình truyền ký tự bị mất kết thúc Chế độ đồng bộ: không cần thiết

+ 1 = tốc độ nhanh.

+ 0 = tốc độ chậm.

Bit 1 TRMT: bit trạng thái dịch truyền thanh ghi.

+ 1 = TSR rỗng.

+ 0 = TSR đầy.

Bit 0 TX9D: bit thứ 9 của truyền dữ liệu, có thể là bit Parity.

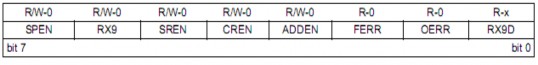

Hình 2.17 Cấu tạo thanh ghi RCSTA

Bit 7 SPEN: bit cho phép Serial Port.

+ 1 = cho phép Serial Port (tức là cấu hình cho RC7/RX/DT và RC6/TX/CK như chân Serial Port).

+ 0 = không cho phép.

Bit 6 RX9: bit cho phép nhận 9 bit.

+ 1 = cho phép nhận 9 bit.

+ 0 = cho phếp nhận 8 bit.

Bit 5 SREN: bit cho phép nhận đơn độc. Chế độ bất đồng bộ không dùng.

Chế độ đồng bộ - Master:

+ 1 = cho phép nhận đơn độc.

+ 0 = không cho phép.

Chế độ đồng bộ - Slave: không cần.

Bit 4 CREN: bit cho phép nhận tiếp tục. Chế độ bất đồng bộ:

+ 1 = cho phép nhận tiếp tục.

Chế độ bất đồng bộ:

+ 1 = cho phép nhận tiếp tục.

+ 0 = không cho phép nhận tiếp tuc.

Chế độ đồng bộ:

+ 1 = cho phép nhận tiếp đến khi bit cho phép CREN bị xóa.

+ 0 = không cho phép nhận tiếp.

Bit 3 ADDEN: bit cho phép phát hiện địa chỉ. Chế độ bất đồng bộ 9 bit (RX9 = 1):

+ 1 = cho phép phat hiện địa chỉ, cho phép nhắc và tải bộ đệm nhận khi RSR<8> được SET.

+ 0 = không cho phép phát hiện địa chỉ, tất cả các Bytes được nhận và bit thứ 9 có thể được sử dụng như là bit Parity.

Bit 2 FERR: bit báo lỗi khung truyền

+ 1 = lỗi khung truyền (có thể được chấp nhận bằng cách đọc thanh ghi RCREG và nhận Byte tiếp the).

+ 0 = không xuất hiện lỗi trong quá trình truyền nhận dữ liệu.

Bit 1 OERR: bit báo lỗi tràn bộ nhớ.

+ 1 = lỗi tràn (có thể xóa bằng cách xóa bit CREN).

+ 0 = không báo lỗi tràn.

Bit 0 RX9D: bit thứ 9 của dữ liệu nhận (có thể là bit parity nhưng phải được tính toán bởi người dùng).

2.6.2 Bộ EUSART hoạt động trong chế độ đồng bộ

Giao diện EUSART đồng bộ được kích hoạt bằng cách set bit SYNC. Cổng giao tiếp nối tiếp vẫn là hai chân RC7/RX/DT, RC6/TX/CK và được cho phép bằng cách set bit SPEN. EUART cho phép hai chế độ truyền nhận dữ liệu là Master mode và Slave mode. Master mode được kích hoạt bằng cách set bit CSRC, Slave mode được kích hoạt bằng cách Clear bit CSRC. Điểm khác biệt duy nhất giữa hai chế độ này là Master mode sẽ lấy xung clock đồng bộ từ bộ tạo xung baud BRG còn Slave mode lấy xung clock đồng bộ từ bên ngoài qua chân RC6/TX/CK. Điều này cho phép Slave mode hoạt động ngay cả khi vi điều khiển đang ở chế độ sleep.

2.7 HOẠT ĐỘNG ĐỊNH THỜI TIMER

2.7.1 Bộ định thời TIMER0

Bộ định thời/bộ đếm Timer 0 có các đặc tính sau:

- Bộ định thời / bộ đếm 8 bit.

- Cho phép đọc và ghi.

- Bộ chia 8 bit lập trình được bằng phần mềm.

- Chọn xung clock nội hoặc ngoại.

- Ngắt khi có sự tràn từ FFh đến 00h.

- Chọn cạnh cho xung clock ngoài.

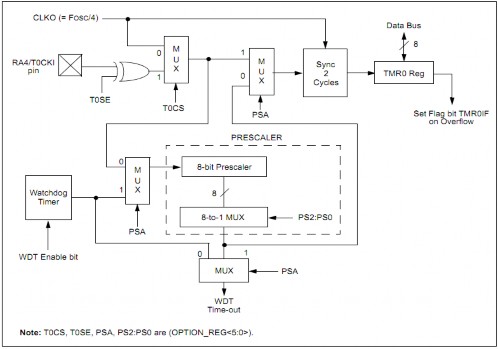

Bên dưới là sơ đồ khối của bộ định thời Timer 0 và bộ chia dùng chung với WDT. Chế độ định thời (Timer) được chọn bằng cách xóa bit T0CS (OPTION_REG<5>) Trong chế độ định thời, bộ định thời Timer 0 sẽ tăng dần sau mỗi chu kỳ lệnh (không có bộ chia). Nếu thanh ghi TMR0 được ghi thì sự tăng sẽ bị ngăn lại sau hai chu kỳ lệnh.

Chế độ đếm (Counter) được chọn bằng cách set bit T0SC (OPTION_REG<5>). Trong chế độ đếm, Timer 0 sẽ tăng dần ở mỗi cạnh lên hoặc cạnh xuống của chân RA4/T0CKI. Sự tăng cạnh được xác định bởi bit Timer0 Source Edge Select, T0SE (OPTION_REG<4>). Bộ chia chỉ được dùng chung qua lại giữa bộ định thời Timer 0 và bộ định thời Watchdog. Bộ chia không cho phép đọc hoặc ghi.

Ngắt TMR0 được phát ra khi thanh ghi TMR0 tràn từ FFh đến 00h đối với 8 bit. Sự tràn này sẽ set bit TMR0IF (INTCON<2>). Ngắt này có thể được giấu đi bằng cách xóa đi bit TMR0IE (INTCON<5>). Bit TMR0IF cần phải được xóa trong chương trình bởi thủ tục phục vụ ngắt của bộ định thời Timer 0 trước khi ngắt này được cho phép lại.

Sơ đồ khối của Timer 0 như sau:

Hình 2.18 Sơ đồ khối bộ định thời Timer 0

Muốn Timer 0 hoạt động ở chế độ Timer ta clear bit T0SC (OPTION_REG<5>), khi đó giá trị thanh ghi TMR0 sẽ tăng theo từng chu kỳ xung đồng hồ (tần số vào