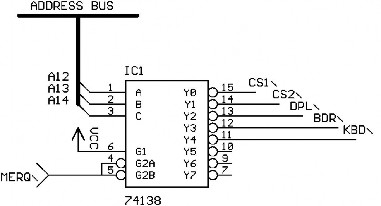

A14 | A13 A12 | A | 11 | A10 | ……A0 | VÙNG NHỚ | TÍN HIỆU | CHỨC NĂNG | |

0 | 0 | 0 | 0 | x x 0 x 1 x x x x x | x x x x x x | …… …… …… ….. x ….. x …… | 0000h – 0FFFh | CS1 | Chọn IC ROM |

0 | 0 | 0 | 1 | 1000h - 17FFh | CS 2 | Chọn IC RAM | |||

0 | 0 | 0 | 1 | 1800h – 1FFFh | Chưa dùng | ||||

0 | 0 | 1 | 0 | 2000h – 2FFFh | DPL | Hiển thị | |||

0 | 0 | 1 | 1 | 3000h - 3FFFh | BDR | Báo hiệu | |||

0 | 1 | 0 | 0 | 4000h - 4FFFh | KBD | Đọc bàn phím |

Có thể bạn quan tâm!

-

Ứng dụng CPU Z80 - Thiết kế và thi công hệ thống báo giờ tự động - 1

Ứng dụng CPU Z80 - Thiết kế và thi công hệ thống báo giờ tự động - 1 -

Ứng dụng CPU Z80 - Thiết kế và thi công hệ thống báo giờ tự động - 2

Ứng dụng CPU Z80 - Thiết kế và thi công hệ thống báo giờ tự động - 2 -

Ưu Nhược Điểm Của Hệ Thống Bao Giờ Tự Động Dùng “Eprom” Và Vi Xử Lí Z80.

Ưu Nhược Điểm Của Hệ Thống Bao Giờ Tự Động Dùng “Eprom” Và Vi Xử Lí Z80. -

_Mạch Kiểm Soát Ngắt (Interupt Controller).

_Mạch Kiểm Soát Ngắt (Interupt Controller). -

Sơ Đồ Khối Mạch Điều Khiển Báo Hiệu.

Sơ Đồ Khối Mạch Điều Khiển Báo Hiệu. -

Lưu Đồ Tổng Quát Chương Trình Main

Lưu Đồ Tổng Quát Chương Trình Main

Xem toàn bộ 105 trang tài liệu này.

Bảng 3 : BẢNG GIẢI MÃ ĐỊA CHỈ BỘ NHỚ.

Mạch giải mã địa chỉ dùng IC 74LS138 có 8 ngõ ra tác động mức thấp. Tín hiệu MERQ từ P tác động vào 2 ngõ vào điều kiện G2A và G2B để điều khiển việc giải mã chọn chip.

Hình 5: SƠ ĐỒ CHI TIẾT MẠCH GIẢI MÃ ĐỊA CHỈ.

2.2.3_Tóm tắt:

Mạch điện bộ nhớ Hệ Thống có cấu tạo như sau:

Hình 6: SƠ ĐỒ CHI TIẾT MẠCH BỘ NHỚ

Các tín hiệu CS1, CS 2 thực hiện chọn IC ROM và IC RAM. Tín hiệu RD

từ P điều khiển việc đọc dữ liệu trong ROM và RAM, tín hiệu WR cho phép P ghi dữ liệu vào RAM.

Giản đồ thời gian các chu kì P đọc và ghi bộ nhớ như hình 7:

VALID ADDRESS

DATA IN

OCK |

CL

A0-A15

MERQ

RD

D0-D7

WR

DATA OUT

D0-D7

Hình 7: CHU KÌ P ĐỌC VÀ GHI BỘ NHỚ.

Hoạt động đọc, ghi bộ nhớ của P như sau:

MERQ | CS | RD | WR | |

Đọc bộ nhớ | L | L | L | H |

Ghi bộ nhớ | L | L | H | L |

Các bộ phận bàn phím, hiển thị và điều khiển báo hiệu thiết kế theo nguyên tắt ánh xạ bộ nhớ. Hoạt động của P truy xuất các bộ phận này như sau:

ĐỊA CHỈ | MERQ | TÍN HIỆU ĐIỀU KHIỂN | |

Hiển thị | 2000h – 2FFFh | L | DPL = L |

Điều khiển báo hiệu | 3000h – 3FFFh | L | BDR = L |

Đọc bàn phím | 4000h – 4FFFh | L | KBD = L |

2.3_ Khảo sát tính chất ngắt NMI :

(NON_ MASKABLE INTERRUPT)

Ngắt NMI (ngắt không thể che bằng phần mềm) của Z80 là ngắt có độ ưu tiên tuyệt đối. Khi có ngắt NMI tác động, chương trình Hệ Thống sẽ tạm dừng công việc hiện tại để thực hiện chương trình phục vụ ngắt NMI bắt đầu tại địa chỉ 0066h.

Với yêu cầu đặt ra là Hệ Thống làm việc với thời gian thực, nên đòi hỏi việc đếm thời gian phải thực hiện chính xác và được ưu tiên hàng đầu. Do đó, ngắt NMI dành cho việc đếm thời gian thực. Tuy nhiên, ngoài hoạt động đếm thời gian thực chương trình Hệ Thống còn phải thực hiện các công việc khác như: phục vụ bàn phím, phục vụ việc báo hiệu cũng như hiển thị. Ngắt NMI không được làm ảnh hưởng đến các hoạt động trên .

Công việc thăm dò ngắt INT và NMI được Z80 thực hiện tại chu kì đồng hồ cuối cùng ở chu kì máy cuối cùng của một chu kì lệnh (gọi là các thời điểm to).

Chu kì máy cuối Chu kì máy lệnh kế

to

Hình 8: GIẢN ĐỒ NHẬN NGẮT NMI

Theo hình 8, nếu có tín hiệu gọi ngắt NMI (hoặc ngắt INT ) xuất hiện tại các thời điểm khác với các thời điểm to thì chương trình Hệ Thống sẽ không nhận được ngắt NMI và chương trình phục vụ ngắt để tạo thời gian thực sẽ không được thực hiện.

Phần mềm Hệ Thống bao gồm nhiều loại lệnh và các lệnh này được thực hiện với số chu kì đồng hồ khác nhau. Do vậy, xung gọi ngắt NMI phải đủ rộng để việc thăm dò ngắt NMI được thực hiện một cách hoàn hảo. Nếu xung gọi ngắt NMI có độ rộng lớn hơn mức cần thiết thì điều gì xảy ra ?

Qua thử nghiệm người viết nhận thấy, khi có ngắt NMI chương trình Hệ Thống tạm dừng công việc hiện tại và thực hiện chương trình phục vụ ngắt NMI , nếu tín hiệu ngắt NMI tiếp tục được giữ ở mức logic thấp thì sau khi chương trình phục vụ ngắt NMI thực hiện xong, P sẽ trở về thực hiện công việc dở dang trước khi phục vụ ngắt mà không bận tâm đến tín hiệu ngắt NMI dù lúc này vẫn

đang ở mức tích cực thấp. Để nhận ngắt trở lại, chân NMI của Z80 phải được kéo lên mức logic cao trước khi có tín hiệu ngắt kế tiếp.

Như vậy có thể nói rằng, khi tín hiệu NMI ở mức thấp và P nhận ngắt thì việc thăm dò ngắt sẽ không được thực hiện cho đến khi tín hiệu NMI lên mức cao. Việc cho tín hiệu NMI lên mức cao trước khi có tín hiệu ngắt kế tiếp tương đương với việc khôi phục hoạt động thăm dò ngắt của P .

Tóm lại, để hoạt động đếm thời gian thực không ảnh hưởng đến các hoạt động khác của Hệ Thống (trong đó có việc P nhận ngắt INT ) thì độ rộng xung gọi ngắt gọi ngắt NMI (đếm thời gian) phải được chọn thích hợp và chương trình phục vụ ngắt NMI phải không được quá dài. Đây là yêu cầu quan trọng đối với hoạt động của Hệ Thống .

2.4_Cấu tạo và nguyên tắt hoạt động các khối mạch:

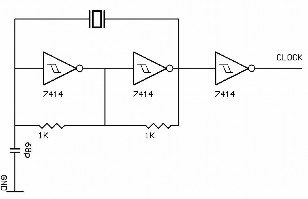

2.4.1_Mạch tạo xung đồng hồ:

Mạch tạo xung đồng hồ có vai trò như quả tim đập nhịp cho hoạt động của Hệ Thống. Viêäc tạo thời gian thực sẽ càng chính xác nếu tần số xung clock cấp cho P càng cao. Tuy nhiên, Hệ Thống sẽ hoạt động khó ổn định ở tần số cao do nhiễu xuất hiện trên đường mạch in. Do vậy, tần số xung clock được chọn sau cho giảm thiểu sai số trong việc tạo thời gian thực và tránh được nhiễu xuất hiện trên mạch in để Hệ Thống hoạt động ổn định. Tần số xung clock được chọn là 500KHz.

Căn cứ vào tần số xung clock đã chọn và tính chất ngắt NMI của P là sẽ nhận ngắt khi phải thực hiện xong lệnh còn đang dang dở ta tính được sai số về thời gian cực đại do việc tạo thời gian thực như sau:

Thời gian thực hiện lệnh dài nhất t = 23x1/fck

= 23/500000

= 0.46s

Sai số trong 1 phút = 60 x t

= 60 x 0.46

= 27,6S

Tính tương tự ta có sai số cực đại trong một năm = 365 x 24 x 60 x 60 x t

= 365 x 24 x 60x 60 x27,6

= 870s

Sai số này là sai số max, thực tế không phải lúc nào tín hiệu gọi ngắt NMI cũng ngay vừa lúc P nhận một lệnh dài nhất nên tần số hoạt động của Hệ Thống = 500KHz là chấp nhận được.

Tần số xung clock này cũng được cấp cho IC 8279 để hiển thị.

Để tận dụng số lượng cổng logic trên mạch cũng như đơn giản trong thiết kế, mạch dao động được thiết kế như sau:

Hình 9: SƠ ĐỒ MẠCH TẠO XUNG ĐỒNG HỒ

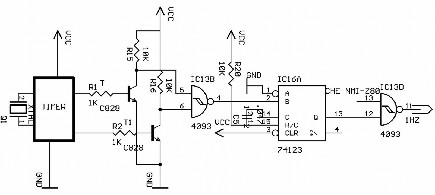

2.4.2_Mạch định thời.

Mạch định thời có nhiệm vụ tạo ra xung nhịp tuần hoàn phục vụ cho việc đếm thời gian thực. Việc đếm thời gian thực đòi hỏi phải thực hiện một cách chính xác và ổn định. Do đó, mạch định thời phải tạo ra tín hiệu định thời có tần số thật chính xác và có tính ổn định cao.

Tín hiệu định thời tác động vào ngắt NMI . Khi có ngắt NMI chương trình tạo thời gian thực sẽ tăng lên 1 đơn vị thời gian (1 giây).

Để có được tín hiệu định thời tần số 1Hz có độ chính xác và tính ổn định cao mặc nhiên không thể sử dụng mạch dao động RC vì giá trị R,C không ổn định theo thời gian cũng như nhiệt độ.

Có thể dùng mạch dao động thạch anh để có được tín hiệu định thời ổn định và chính xác. Tuy nhiên, giá trị thạch anh bán ngoài thị trường ít nhất cũng vài trăm KHz, cho nên phải tốn thêm mạch chia tần số thì mới có được tín hiệu định thời tần số 1Hz.

Chính vì vậy người viết chọn mạch dao động trong đồng hồ GIMIKO, đây là mạch chuyên dùng nên đảm bảo được tính ổn định và chính xác của tín hiệu định thời.

Hình 10: SƠ ĐỒ MẠCH ĐỊNH THỜI.

Do mạch dao động sử dụng nguồn 1,5V nên tín hiệu định thời ở ngõ ra sẽ được khuyếch đại lên cho phù hợp với mức logic của mạch số. Sau đó, tín hiệu định thời sẽ được giới hạn độ rộng xung trước khi đưa đến chân NMI của Z80 bằng một mạch đơn ổn (Mono Multivibrator).

Độ rộng xung gọi ngắt NMI được chọn phụ thuộc vào thời gian thực hiện lệnh dài nhất trong chương trình Hệ Thống. Thời gian thực hiện lệnh dài nhất của Z80 là 23x1/fck(giây) để bảo đảm P nhận được ngắt mỗi khi có tín hiệu ngắt NMI = 0. Độ rộng xung gọi ngắt phải thỏa:

> 23x1/fck = 0.46s

IC 74LS123 có công thức tính độ rộng xung như sau:

= 0,45xRxC

Với R = 1K, C = 0.047f

Ta có = 0,45x 1000x0.047x10-6 = 21,1s

xấp xỉ 45.1 lần thời gian thực hiện lệnh dài nhất của P, giá trị này của

thỏa mãn yêu cầu đặt ra.

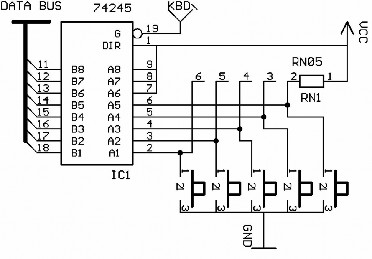

2.4.3_Mạch bàn phím (Keyboard):

Người sử dụng dùng bàn phím để điều chỉnh thời gian (Settime), đặt các thời điểm báo hiệu đột xuất (Hottime), đặt các thời điểm cấm báo hiệu (Skiptime), xem hoặc xóa nội dung bảng Hotime/Skiptime.

Để đáp ứng các yêu cầu trên, bàn phím sẽ có 5 phím với tên gọi như sau : Ins, +, -, Del/Date và Ok chức năng từng phím do phần mềm qui định. Cách sử dụng bàn phím được mô tả chi tiết ở phần “Mô tả Hệ Thống và hướng dẫn sử dụng”.

Bàn phím được thiết kế theo nguyên tắc ánh xạ bộ nhớ, P sẽ xem bàn phím như 1 byte nhớ. Bàn phím có địa chỉ thuộc vùng nhớ từ 4000h đến 4FFFh. P dùng tín hiệu điều khiển để truy xuất bàn phím. Các phím ấn khác nhau sẽ làm cho byte nhớ có nội dung khác nhau tương ứng với chức năng khác nhau của mỗi phím. Chu kì P đọc bàn phím như hình 11.

CLOCK

A0-A15

MERQ

D0-D7

Hình 11: CHU KÌ P ĐỌC BÀN PHÍM.

Tín hiệu MERQ từ P sẽ hiệu lực hóa việc giải mã địa chỉ tạo ra tín hiệu để P đọc bàn phím.

Bàn phím có cấu tạo gồm một IC đệm 8 bit 3 trạng thái và 5 Switch như sau:

Hình 12: SƠ ĐỒ CHI TIẾT MẠCH BÀN PHÍM .

IC 74LS245 được dùng làm mạch đệm 8 bit 3 trạng thái nên bàn phím có tối đa 8 phím. Hiện tại bàn phím gồm 5 phím, P dùng tín hiệu điều khiển KBD tác động vào chân G của IC 74LS245 để đọc bàn phím. Khi không có phím nào được