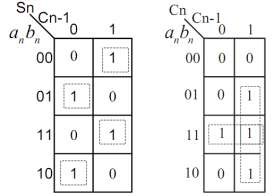

Hình 1. 44. Bìa các nô của bộ cộng toàn phần Phương trình trạng thái hàm Sn và Cn

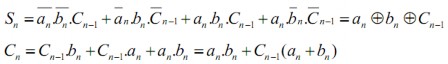

Sơ đồ mạch cộng toàn phần

Hình 1. 45. Sơ đồ mạch cộng toàn phần

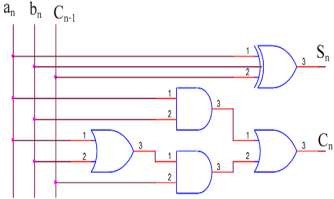

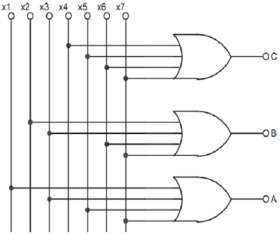

c) Thiết kế mạch mã hóa nhị phân từ 8 sang 3

Hình 1. 46. Sơ đồ khối mạch mã hóa nhị phân từ 8 sang 3 Trong đó

- x0, x1,. . ., x7 là các ngò vào tín hiệu

- A, B, C là các ngò ra

Mạch mã hóa nhị phân thực hiện biến đổi tín hiệu ngò vào thành môt từ mã nhị phân tương ứng ở ngò ra cụ thể như sau:

1→001 | 2→ 010 | 3→ 011 | |

4→100 | 5→101 | 6→ 110 | 7→ 111 |

Có thể bạn quan tâm!

-

Kiến trúc máy tính - 5

Kiến trúc máy tính - 5 -

Các Phép Toán Và Định Lý Của Đại Số Boolean

Các Phép Toán Và Định Lý Của Đại Số Boolean -

Hàm Logic Và Phương Pháp Biểu Diễn Hàm Logic Các Phương Pháp Biểu Diễn Hàm Logic

Hàm Logic Và Phương Pháp Biểu Diễn Hàm Logic Các Phương Pháp Biểu Diễn Hàm Logic -

Kiến trúc máy tính - 9

Kiến trúc máy tính - 9 -

Kiến trúc máy tính - 10

Kiến trúc máy tính - 10 -

Kiểu Định Vị Gián Tiếp Bằng Thanh Ghi + Độ Dời

Kiểu Định Vị Gián Tiếp Bằng Thanh Ghi + Độ Dời

Xem toàn bộ 233 trang tài liệu này.

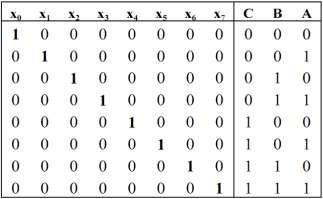

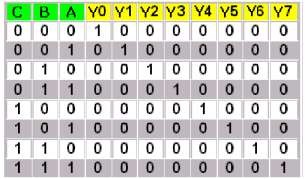

Chọn mức tác động tích cực ở ngò vào là mức logic 1, ta có bảng sự thật mô tả hoạt động của mạch như sau:

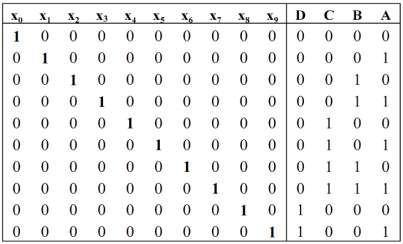

Bảng 1. 14. Bảng sự thật mạch mã hóa nhị phân từ 8 sang 3

Khi một ngò vào ở trạng thái tích cực (mức logic 1) và các ngò vào không được tích cực nhận mức logic 0. Thì ngò ra xuật hiện từ mã tương ứng. Cụ thể khi x0=1, các đầu ra còn lại x1= x2= x3 = x4 = x5 = x6 = x7 = 0, thì từ mã ngò ra là 000. khi x1=1 các đầu ra còn lại x0= x2=x3 = x4 = x5 = x6 = x7 = 0, thì từ mã ngò ra nhận giá trị 01,..vv…

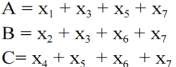

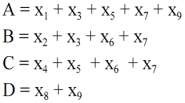

Từ bảng trạng thái ta có phương trình trạng thái ngò ra như sau:

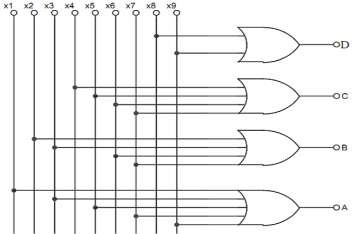

Từ phương trình trạng thái ngò ra ta có sơ đồ mạch logic thực hiện quả trình mã hóa như sau:

Hình 1. 47. Mạch logic dùng phần tử OR

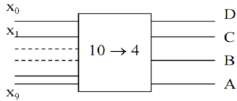

d) Thiết kế mạch mã hóa thập phân 10-4

Hình 1. 48. Sơ đô đồ khối mạch mã hóa thập phân

Trong đó

- x0, x1,. . ., x9 là các ngò vào tín hiệu

- A, B, C, D là các ngò ra

Mạch mã hóa nhị phân thực hiện biến đổi tín hiệu ngò vào thành môt từ mã nhị phân tương ứng ở ngò ra cụ thể như sau:

0 →0000 1→0001 2→ 0010 3→ 0011 4→ 0100

5→0101 6→ 0110 7→ 0111 8→1000 9→1001

Chọn mức tác động tích cực ở ngò vào là mức logic 1, ta có bảng sự thật mô tả hoạt động của mạch như sau:

Bảng 1. 15. Bảng bảng sự thật mạch mã hóa nhị phân từ 10 sang 4

Từ phương trình trạng thái tối giản ta có sơ đồ mạch logic dùng phần tử OR như sau:

Hình 1. 49. Sơ đồ mạch mã hóa thập phân dùng OR

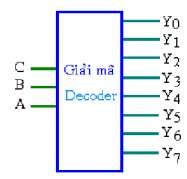

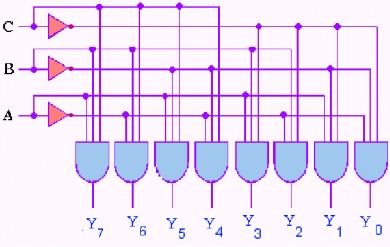

e) Giải mã 3 sang 8

Mạch giải mã 3 đường sang 8 đường bao gồm 3 đường vào tạo nên 8 tổ hợp trạng thái, ứng với mỗi tổ hợp trạng thái được áp vào sẽ có 1 đường ra được tác động.

Hình 1. 50. Khối giải mã 3 sang 8

Bảng 1. 16. Bảng chân lý mạch giải mã 3 sang 8

Từ bảng chân lý ta có thể vẽ được sơ đồ mạch logic của mạch giải mã trên

Hình 1. 51. Cấu trúc mạch giải mã 3 sang 8

1.7.2. Mạch tuần tự

Trigơ (Flip - Flop) là phần tử cơ bản nhất để từ đó chế tạo ra các mạch dãy (mạch logic có nhớ). Mạch Trigơ thuộc loại mạch không đồng bộ có hai trạng thái ổn định bền theo thời gian ứng với hai mức logic "1" và "0". Trạng thái của Trigơ có thể thay đổi khi tác động xung lên các đầu vào. Trạng thái tương lai của Trigơ không những phụ thuộc vào các biến vào mà còn phụ thuộc vào trạng thái hiện tại. Khi ngừng

tác động xung lên các đầu vào, trạng thái Trigơ giữ nguyên, với đặc điểm này các mạch Trigơ được dùng để lưu trữ thông tin dưới dạng mã nhị phân.

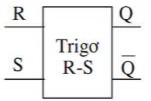

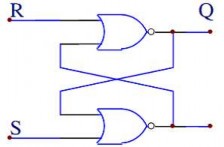

a) Trigơ R-S không đồng bộ

Là loại Trigơ cơ bản nhất để từ đó tạo ra các loại Trigơ khác gồm có 2 đầu vào là R, S và hai đầu ra ![]() với:

với:

- ![]() : Đầu ra chính thường được sử dụng.

: Đầu ra chính thường được sử dụng.

- ![]() : Đầu ra phụ, luôn thoả mãn

: Đầu ra phụ, luôn thoả mãn

- R (Reset): Đầu vào xoá.

- S (Set): Đầu vào thiết lập.

Ý tưởng thiết kế trigơ R-S không đồng bộ theo các điều kiện sau:

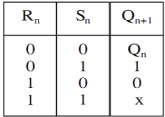

+ Rn = Sn = 0, trạng thái của trigơ giữ nguyên → Qn+1 = Qn.

+ Rn = 0; Sn = 1 đầu ra trigơ nhận giá trị "1"→ Qn+1 = 1.

+ Rn = 1; Sn = 0 đầu ra trigơ nhận giá trị "0" → Qn+1 = 0.

+ Rn = 1; Sn = 1 đây là trạng thái cấm, trạng thái Trigơ là không xác định, trong bảng trạng thái được đánh dấu bằng dấu "x".

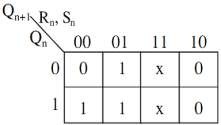

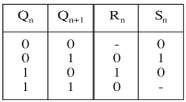

Hoạt động của trigơ R-S tuân theo bảng trạng thái nh hình vẽ.

- n: Trạng thái hiện tại

- n + 1: Trạng thái tương lai.

- "-": Giá trị tuỳ chọn - có thể lấy giá trị "1" hoặc "0".

- x: Trạng thái cấm tại đó giá trị của hàm ra là không xác định.

Sơ đồ mô phỏng Bảng trạng thái

Hình 1. 52. Sơ đồ mô phỏng và bảng trạng thái của Trigơ R-S không đồng bộ

Bảng chuyển tiếp Bảng đầu vào kích

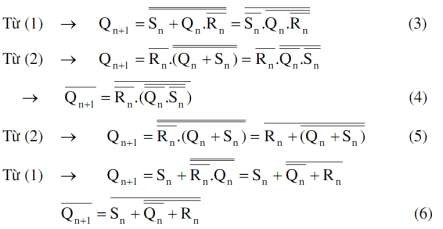

Hình 1. 53. Bảng chuyển tiếp và bảng đầu vào kích của Trigơ R-S không đồng bộ Thực hiện nhóm các ô có giá trị “1” trong bảng trạng thái (dạng tuyển) ta có:

Nhóm các ô có giá trị “0” trong bảng trạng thái (dạng hội) ta có:

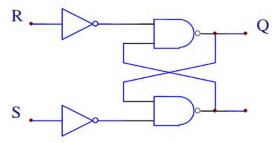

Hình 1. 54. Sơ đồ Trigơ R-S dùng phần tử NAND

Hình 1. 55. Sơ đồ Trigơ R-S dùng phần tử NOR

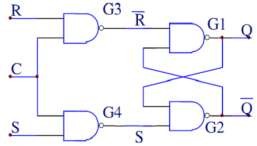

b) Trigơ R-S đồng bộ

Người ta muốn Trigơ chỉ phản ứng vào những thời điểm xác định, điều này được thực hiện bằng cách đưa thêm tới đầu vào tín hiệu phụ C được gọi là tín hiệu đồng bộ. Khi C ="0" thì R = S = 1 trạng thái Trigơ giữ nguyên còn C ="1" hoạt động của sơ đồ giống Trigơ R-S không đồng bộ như đã phân tích ở phần trên.

Hình 1. 56. Trigơ R-S đồng bộ

CÂU HỎI ÔN TẬP CHƯƠNG 1

Câu 1:

Trình bày khái niệm máy tính và kiến trúc máy tính.

Câu 2:

Dựa vào tiêu chuẩn nào để phân chia máy tính thành các thế hệ? Trình bày các đặc trưng cơ bản của máy tính qua các thế hệ.

Câu 3:

Trình bày cấu trúc và các chức năng cơ bản của máy tính.

Câu 4:

Nêu các đặc điểm chính và cấu trúc tổng quát của máy tính Von-Neumann.

Câu 5:

Nêu bảng chân lý, ký hiệu của các cổng logic: AND, OR, NOT, XOR, NOR, NAND và cách biểu diễn qua lại giữa các cổng.

Câu 6:

Chuyển đổi các số trong hệ đếm cơ số 10 sau đây sang hệ đếm cơ số 2 và hệ đếm cơ số 16.

a) 345,125D b) 675,35D

Câu 7:

Chuyển đổi các số trong hệ đếm cơ số 16 sau đây sang hệ đếm cơ số 2 và hệ đếm cơ số 10.

a) DF4H

b) 13AFH

Câu 8:

Chuyển đổi các số trong hệ đếm cơ số 2 sau đây sang hệ đếm cơ số 10 và hệ đếm cơ số 16.

a) 100110111B

b) 1100101101001100,101B

Câu 9:

Đổi các số sau từ hệ thập phân sang hệ nhị phân: a) 28 b) 89 c) 294

d) 34,5 e) 55,25 f) 46,3125

Câu 10:

Đổi các số sau từ hệ nhị phân sang hệ thập phân: a) 11001 b) 111001

c) 10111011 d) 10001001

Câu 11:

Đổi các số sau từ hệ thập phân sang hệ thập lục: a) 68 b) 29 c) 215

Câu 12:

Đổi các số sau từ hệ thập lục sang hệ thập phân:

a) AF b) 123 c) 10D

Câu 13:

Biểu diễn các số sau dùng dấu và độ lớn (8 bit): a) +69 b) +105 c) -28 d) -121

Câu 14:

Biểu diễn các số sau dùng dấu và độ lớn (16 bit): a) +109 b) +105 c) -98 d) -131

Câu 15:

Biểu diễn các số sau dùng mã bù 2 (8 bit – không dấu): a) 57 b) 48 c) 98 d) 131

Câu 15:

Biểu diễn các số sau dùng mã bù 2 (8 bit – có dấu): a) +57 b) +48 c) -98 d) -31

Câu 16:

Biểu diễn các số sau dùng mã bù 2 (16 bit – không dấu): a) 157 b) 108 c) 128 d) 35

Câu 17:

Biểu diễn các số sau dùng mã bù 2 (16 bit – có dấu): a) 137 b) 119 c) -113 d) -53

Câu 18:

Có các biểu diễn sau (dùng dấu và độ lớn), hãy xác định giá trị của chúng: a) 0100 1011 b) 1001 1100

c) 0000 0000 1001 0010; d) 1000 0000 0110 1100

Câu 19:

Có các biểu diễn sau (dùng mã bù 2- không dấu), hãy xác định giá trị: a) 0100 0001 b) 1010 0100

c) 0000 0000 1001 0010; d) 1000 0000 0010 0100

Câu 20:

Có các biểu diễn sau (dùng mã bù 2 - có dấu), hãy xác định giá trị của chúng: a) 0100 1011 b) 1101 1100