Trong các chip DRAM trước đây mạch điện bổ sung để thực hiện làm tươi thường ở ngoài chip nhớ. Ngày nay các mạch thực hiện làm tươi thường được chế tạo nằm ngay bên trong chip nhớ, nhờ đó chip nhớ loại này vừa có dung lượng cao vừa có giao diện đơn giản, chúng được gọi là quasi-static RAM.

4.3.1.2. Bộ nhớ chính RAM

Bộ nhớ chính RAM của máy tính được chế tạo theo công nghệ DRAM, vì vậy đặc trưng của bộ nhớ RAM là nó có thể đọc dữ liệu từ bộ nhớ và ghi một cách dễ dàng và nhanh chóng dữ liệu mới vào bộ nhớ. Quá trình đọc và ghi đều được thực hiện bằng tín hiệu điện. RAM cần phải được cung cấp bằng một nguồn không đổi. Nếu nguồn bị ngắt thì dữ liệu bị mất. Do vậy RAM là bộ nhớ tạm thời.

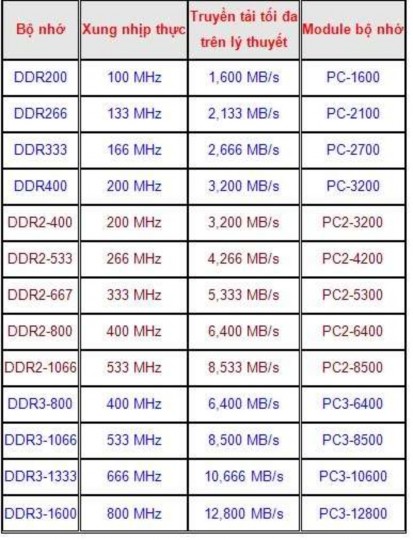

Hiện nay bộ nhớ RAM có 3 loại phổ biến là DDR, DDR2 và DDR3 dựa trên thiết kế SDRAM (bộ nhớ truy cập ngẫu nhiên động đồng bộ - Synchronous Dynamic Random Access Memory), tức là sử dụng tín hiệu xung nhịp để đồng bộ hóa mọi thứ. DDR là viết tắt của Double Data Rate (tốc độ dữ liệu gấp đôi), tức truyền được hai khối dữ liệu trong một xung nhịp. Như vậy bộ nhớ DDR có tốc độ truyền dữ liệu cao gấp đôi so với những bộ nhớ có cùng tốc độ xung nhịp nhưng không có tính năng này (được gọi là bộ nhớ SDRAM, hiện không còn sử dụng cho PC nữa). Nhờ tính năng này mà trên nhãn của những thanh nhớ thường ghi tốc độ tốc gấp đôi so với tốc độ đồng hồ xung nhịp thực. Ví dụ bộ nhớ DDR2 - 800 làm việc ở tốc độ 400 MHz, DDR2

- 1066 và DDR3 - 1066 làm việc ở tốc độ 533 MHz, DDR3 - 1333 ở 666.6 MHz ...

Trên mỗi thanh RAM (mô-đun nhớ) đều có các chip nhớ (có thể là 4, 8, 16 chip nhớ), các chip nhớ được nối với nhau thông qua vi mạch. Dung lượng của bộ nhớ RAM chính là tổng dung lượng của các chip nhớ này. Trong ví dụ ở hình 4.5 là một bộ nhớ RAM của hãng Kingston, thuộc thế hệ DDRAM2, có dung lượng 2GB và có 16 chip nhớ (mỗi mặt của RAM có 8 chip nhớ, mỗi chip nhớ có dung lượng 128MB).

Hình 4. 5. Bộ nhớ DDRAM2

Những thanh nhớ (mô-đun) sử dụng một cái tên khác: PCx-zzzz, trong đó x là thế hệ công nghệ, còn zzzz là tốc độ truyền tải tối đa trên lý thuyết (còn gọi là băng thông tối đa). Con số này cho biết bao nhiêu byte dữ liệu có thể được truyền từ mạch điều khiển bộ nhớ sang mô-đun bộ nhớ trong mỗi xung nhịp đồng hồ .

Bài toán này rất dễ giải bằng cách nhân xung nhịp DDR tính bằng MHz với 8, ta sẽ có tốc độ truyền tải tối đa trên lý thuyết tính bằng MB/giây. Ví dụ, bộ nhớ DDR2- 800 có tốc độ truyền tải tối đa trên lý thuyết là 6,400 MB/giây (800 x 8) và mô-đun bộ nhớ mang tên PC2-6400. Trong một số trường hợp, con số này được làm tròn. Ví dụ như bô nhớ DDR3-1333 có tốc độ truyền tải tối đa trên lý thuyết là 10,666 MB/giây nhưng mô-đun bộ nhớ của nó lại có tên PC3-10666 hoặc PC3-10600 tùy nhà sản xuất.

Những con số này chỉ là số tối đa trên lý thuyết, và trên thực tế chúng không bao giờ đạt đến, bởi bài toán chúng ta đang tính có giả thiết rằng bộ nhớ sẽ gửi dữ liệu đến mạch điều khiển bộ nhớ theo từng xung nhịp một, mà điều này thì không xảy ra. Mạch điều khiển bộ nhớ và bộ nhớ cần trao đổi lệnh (ví dụ như lệnh hướng dẫn bộ nhớ gửi dữ liệu được chứa tại một vị trí nhất định) và trong suốt thời gian này bộ nhớ sẽ không gửi dữ liệu. Trên đây là lý thuyết cơ bản về bộ nhớ DDR. Sau đây chúng ta sẽ so sánh 3 loại bộ nhớ RAM này.

Hình 4. 6. Hình dáng các loại DDRAM

Tốc độ (Speed)

Đây là thông số được người dùng quan tâm nhất. Đối với DDR thì có hai cách gọi theo tốc độ MHz hoặc theo băng thông.

Ví dụ, khi nói DDR333 tức là thanh RAM đó mặc định hoạt động ở tốc độ 333MHz nhưng cách gọi PC2700 thì lại nói về băng thông RAM, tức là khi chạy ở tốc độ 333Mz thì nó sẽ đạt băng thông là 2700MB/s (trên lý thuyết). Thường ở Việt Nam thông dụng các loại RAM có bus 333 và 400, những loại có bus cao hơn thường xuất hiện ở những loại cao cấp như Kingston HyperX, Corsair, Mushkin LV.

Một trong những khác biệt chính giữa DDR, DDR2 và DDR3 là tốc độ truyền dữ liệu lớn nhất của từng thế hệ. Dưới đây là danh sách tốc độ chung nhất cho từng thế hệ. Một số nhà sản xuất đã tạo ra được những loại chip lớn hơn cả tốc độ trong bảng.

Ví dụ như các bộ nhớ đặc biệt hướng tới giới overclock. Những xung nhịp có đuôi 33 hoặc 66MHz thực ra đã được làm tròn (từ 33.3333 và 66.6666).

Hình 4. 7. Tốc độ của DDR2, DDR3

Điện áp

Bộ nhớ DDR3 hoạt động ở điện áp thấp hơn so với DDR2. DDR2 lại dùng điện áp thấp hơn DDR. Như vậy bộ nhớ DDR3 sẽ tiêu thụ ít điện hơn DDR2, và DDR2 tiêu thụ ít hơn DDR. Thường thì bộ nhớ DDR sử dụng điện 2.5 V, DDR2 dùng điện 1.8 V và DDR3 là 1.5 V (mặc dù các mô-đun cần đến 1.6 V hoặc 1.65 V rất phổ biến và những chip chỉ yêu cầu 1.35 V trong tương lai cũng không phải là hiếm). Một số mô- đun bộ nhớ có thể yêu cầu điện áp cao hơn trong bảng, nhất là khi bộ nhớ hỗ trợ hoạt động ở tốc độ xung nhịp cao hơn tốc độ chính thức (ví dụ như bộ nhớ để overclock).

Hình 4. 8. Điện áp của DDR2, DDR3

Thời gian trễ

CAS Latency là khái niệm mà người dùng thắc mắc nhiều nhất. Trước đây, khi chọn RAM, người mua thường chỉ quan tâm tới tốc độ hoạt động như 100MHz hay 133MHz. Thời gian gần đây, khái niệm CAS đang dần được người dùng để ý bởi nó đóng vai trò khá quan trọng vào tốc độ xử lý tổng thể của hệ thống; đặc biệt trong ép xung. CAS là viết tắt của “Column Address Strobe” (địa chỉ cột). Một thanh DRAM được coi như một ma trận của các ô nhớ và mỗi ô nhớ sẽ có địa chỉ cột CAS và địa chỉ hàng RAS (Row Adress Strobe). Nhưng do nguyên lý hoạt động của DRAM là truyền dữ liệu xuống chân nên RAS thường không quan trọng bằng CAS.

Thời gian trễ là khoảng thời gian mà mạch điều khiển bộ nhớ phải đợi từ lúc yêu cầu lấy dữ liệu cho đến lúc dữ liệu thực sự được gửi tới đầu ra. Nó còn được gọi là CAS Latency hoặc đơn giản là CL. Con số này được viết theo đơn vị chu kỳ xung nhịp. Ví dụ một bộ nhớ có CL3 tức là mạch điều khiển bộ nhớ phải đợi 3 chu kỳ xung nhịp từ lúc truy vấn cho đến khi dữ liệu được gửi. Với một bộ nhớ CL5, mạch điều khiển bộ nhớ phải đợi 5 chu kỳ xung nhịp Vì thế cần sử dụng những mô-đun có CL thấp nhất có thể.

Để hiểu khái niệm này, chúng ta sẽ cùng điểm nhanh qua cách thức bộ nhớ làm việc, đầu tiên chipset sẽ truy cập vào hàng ngang (ROW) của ma trận bộ nhớ thông qua việc đưa địa chỉ vào chân nhớ (chân RAM) rồi kích hoạt tín hiệu RAS. Chúng ta sẽ phải chờ khoảng vài xung nhịp hệ thống (RAS to CAS Delay) trước khi địa chỉ cột được đặt vào chân nhớ và tín hiệu CAS phát ra. Sau khi tín hiệu CAS phát đi, chúng ta tiếp tục phải chờ một khoảng thời gian nữa (đây chính là CAS Latency) thì dữ liệu sẽ được tìm thấy. Điều đó cũng có nghĩa là với CAS 2, chipset phải chờ 2 xung nhịp trước khi lấy được dữ liệu và với CAS3, thời gian chờ sẽ là 3 xung nhịp hệ thống.

Tuy nhiên, CAS2 không có nghĩa nhanh hơn CAS3 tới 33 vì có nhiều yếu tố ảnh hưởng đến hiệu năng tổng thể của bộ nhớ.

Hình 4. 9. Thời gian trễ của DDR2, DDR3

Cuối cùng ta sẽ đến với sự khác biệt về thiết kế bên ngoài. Mô-đun bộ nhớ cho từng thế hệ DDR có sự khác nhau về thông số và không thể cài mô-đun DDR2 lên khe cắm DDR3 được. Ta cũng không thể nâng cấp từ DDR2 lên DDR3 mà không thay thế bo mạch chủ và sau đó là CPU, hay tương tự với DDR và DDR2. Mô-đun DDR2 và DDR3 có cùng số chân, tuy nhiên khe cắm nằm ở vị trí khác nhau.

Hình 4. 10. Số chân nối của DDR, DDR2, DDR3

4.3.2. Bộ nhớ ROM

ROM (Read Only Memory) là bộ nhớ giữ thông tin cố định, không thay đổi nội dung ngay cả khi ngắt nguồn điện nuôi. ROM chứa chương trình BIOS, có trên mainboard và các thiết bị ngoại vi. Có thể chia ROM thành 3 loại chính sau:

- ROM mặt nạ (MROM - Maskable ROM), nội dung của nó được cố định trong quá trình chế tạo vi mạch và không thể thay đổi được sau đó.

- ROM có thể nạp chương trình (PROM – Programmable ROM), là loại ROM mà người sử dụng có thể sử dụng một thiết bị chuyên dụng để nạp nội dung cho nó, việc này thường được gọi là “đốt ROM”. Sau khi đã nạp chương trình, nội dung của PROM cũng không thể thay đổi được nữa.

- ROM có thể xóa (Erasable ROM), là loại ROM mà người sử dụng có thể nạp nội dung cho nó bằng thiết bị chuyên dụng, tuy nhiên người sử dụng sau này có thể xóa nội dung cũ để ghi nội dung mới. Loại ROM này thường là EPROM, EAROM.

4.3.2.1. ROM mặt nạ

Với ROM được lập trình bằng mặt nạ, nhà sản xuất đã ghi (lập trình) các vị trí nhớ của nó theo yêu cầu của khách hàng. Một phím âm bản, gọi là mặt nạ được sử dụng để kiểm soát các mối nối điện trên chip.

Vì mặt nạ rắt đắt nên loại ROM này không được mang lại hiệu quả kinh tế. Nhược điểm của loại ROM này là nó không cho phép lập trình lại, vì vậy nó là dạng ROM đúng nghĩa. Tuy nhiên ROM được lập trình bằng mặt nạ vẫn chỉ là phương pháp tiết kiệm nhất khi cần trang bị số lượng lớn ROM cùng loại.

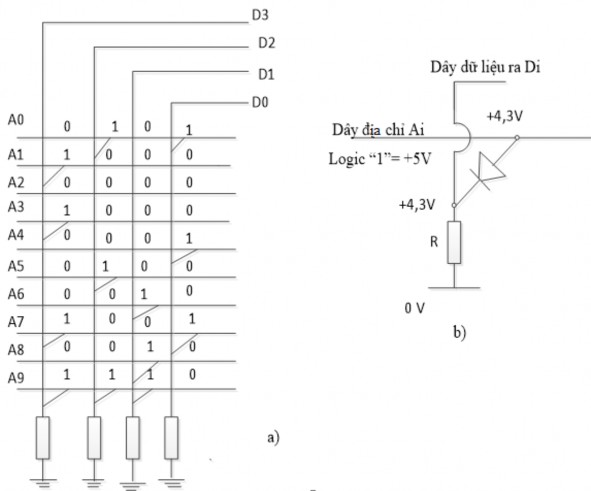

ROM mặt nạ thường tổ chức dưới dạng ma trận. Trạng thái có hay không có đi- ốttại vị trí (i,j) của ma trận được sử dụng để biểu diễn 1 bit dữ liệu là 1 hay 0. Mỗi hàng i của ma trận đi-ốt giống như 1 thanh ghi lưu trữ 1 từ (word), các dây địa chỉ Ai được sử dụng để chọn lấy 1 từ, đưa nội dung của nó ra ngoài qua các dây dữ liệu ra.

Hình 4.11b là 1 “ô nhớ” của ma trận đi-ốt.

Hình 4. 11. Cấu tạo MROM

Việc ghi chương trình cho ROM được thực hiện bằng cách loại bỏ hoặc để lại đi-ốt ở giao điểm của dây hàng và dây cột của ma trận.

• Nếu đi-ốt tại hàng i, cột j được giữ lại, khi mức điện áp trên dây địa chỉ là 1 (cao), đi-ốt được phân cực thuận sẽ có điện trở rất nhỏ, vì vậy Dj=Ai=1.

• Nếu đi-ốt tại hàng i, cột j đã bị loại bỏ, dù mức điện áp trên dây địa chỉ là cao, nó cũng không ảnh hưởng tới dây dữ liệu ra Dj lúc này được “nối đất” (low,0) qua một điện trở.

Bảng 4. 1. Bảng chân lý của MROM

A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D3 | D2 | D1 | D0 | |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

Có thể bạn quan tâm!

-

Hoạt Động Của Cpu Nguyên Lý Hoạt Động

Hoạt Động Của Cpu Nguyên Lý Hoạt Động -

Kiến trúc máy tính - 15

Kiến trúc máy tính - 15 -

Bộ Nhớ Và Các Hệ Thống Lưu Trữ

Bộ Nhớ Và Các Hệ Thống Lưu Trữ -

Kiến trúc máy tính - 18

Kiến trúc máy tính - 18 -

Kiến trúc máy tính - 19

Kiến trúc máy tính - 19 -

Các Phương Pháp Ánh Xạ Giữa Cache Và Bộ Nhớ Chính

Các Phương Pháp Ánh Xạ Giữa Cache Và Bộ Nhớ Chính

Xem toàn bộ 233 trang tài liệu này.

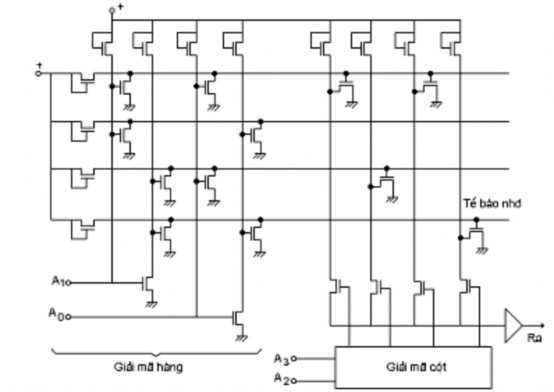

Các công nghệ MOS và công nghệ lưỡng cực đều được sử dụng để chế tạo ROM. Thay cho mỗi đi-ốt người ta có thể dùng 1 transistor lưỡng cực (Bo-polar transistor) hay 1 transistor đơn cực (MOSFET), tuy vậy nguyên tắc vẫn không có gì thay đổi. Thời gian truy cập giữa 2 loại ROM lưỡng cực và MOS là khác nhau, Rom lưỡng cực (Bo-polar ROM) là: 50-90ns, nó có tác động nhanh hơn, khả năng kích thích tốt hơn. Đối với ROM theo công nghệ MOS (MOS ROM) thời gian tác động lớn gấp 10 lần (chậm hơn), nhưng kích thước nhỏ hơn, tiêu thụ ít năng lượng hơn.

Hình 4. 12. Bộ nhớ MROM có dung lượng 16x1 sử dụng Transistor MOS

4.3.2.2. PROM – ROM có thể nạp chương trình

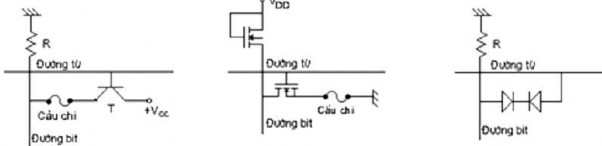

Có cấu tạo giống MROM nhưng ở mỗi vị trí nhớ đều có linh kiện nối với cầu chì. Như vậy khi xuất xưởng các ROM này đều chứa cùng một loại bit (gọi là ROM trắng), lúc sử dụng người lập trình thay đổi các bit mong muốn bằng cách phá vỡ cầu chì ở các vị trí tương ứng với bit đó. Một khi cầu chì đã bị phá vỡ thì không thể nối lại được do đó loại ROM này cho phép lập trình một lần duy nhất để sử dụng, nếu bị lỗi không thể sửa chữa được (hình 4.13).

Người ta có thể dùng 2 đi-ốt mắc ngược chiều nhau, mạch không dẫn điện, để tạo bit 0 khi lập trình thì một đi-ốt bị phá hỏng tạo mạch nối tắt, đi-ốt còn lại dẫn điện cho bit 1.

Hình 4. 13. Bộ nhớ PROM

Thiết bị ghi PROM (PROM Programmer hay PROM Write)

Việc ghi PROM đòi hỏi những mạch cung cấp dòng điện đủ lớn để đốt cháy cầu chì ở những bit mong muốn. Các bộ ghi PROM thường là hệ vi xử lí chuyên dụng. Đó là thiết bị tạo ra địa chỉ, số liệu và xung dòng điện ghi cần thết đẻ làm chảy các cầu chì. Mỗi bộ ghi PROM có thể ghi 1 hay 1 họ PROM, có những bộ ghi PROM vạn năng có thể ghi bất kì loại PROM nào bằng cách sử dụng 1 mô-đun riêng. Mô-đun này giúp cho bộ ghi PROM thích hợp ở mức xung ghi, dòng điện và bố trí chân với 1 mạch PROM cụ thể.

Giá thành ghi PROM đắt hơn ghi ROM nên PROM chỉ thuận lợi cho những ứng dụng với số lượng nhỏ.

4.3.2.3. ROM lập trình được, xóa được bằng tia U.V.

(Ultra Violet Erasable Programmable ROM, U.V. EPROM)

Đây là loại ROM rất tiện cho người sử dụng vì có thể dùng được nhiều lần bằng cách xóa và nạp lại. Cấu tạo của tế bào nhớ của U.V. EPROM dựa vào một transistor MOS có cấu tạo đặc biệt gọi là FAMOS (Floating Gate Avalanche Injection MOS), EPROM – ROM có thể xóa và ghi lại