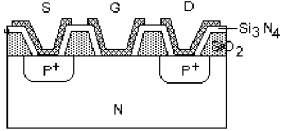

Hình 4. 14. Cấu tạo EPROM

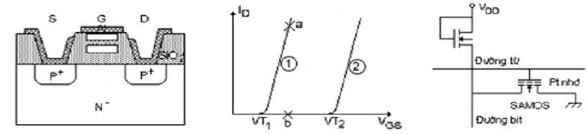

Trên nền chất bán dẫn N pha loãng, tạo 2 vùng P pha đậm (P+) nối ra ngoài cho 2 cực S (Source) và D (Drain). Trong lớp cách điện SiO2 giữa 2 cực người ta cho vào một thỏi Silicon không nối với bên ngoài và được gọi là cổng nổi. Khi nguồn VDD, phân cực ngược giữa cực nền và Drain còn nhỏ, transistor không dẫn, nhưng nếu tăng VDD đủ lớn, hiện tượng thác đổ (avalanche) xảy ra, electron đủ năng lượng chui qua lớp cách điện tới bám vào cổng nổi. Do hiện tượng cảm ứng, một điện lộ P hình thành nối hai vùng bán dẫn P+, transistor trở nên dẫn điện. Khi cắt nguồn, transistor tiếp tục

dẫn điện vì electron không thể trở về để tái hợp với lỗ trống.

Mỗi tế bào nhớ EPROM gồm một transistor FAMOS nối tiếp với một transistor MOS khác mà ta gọi là transistor chọn, như vậy vai trò của FAMOS giống như là một cầu chì nhưng có thể phục hồi được.

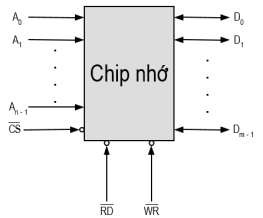

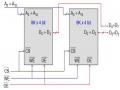

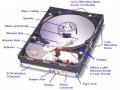

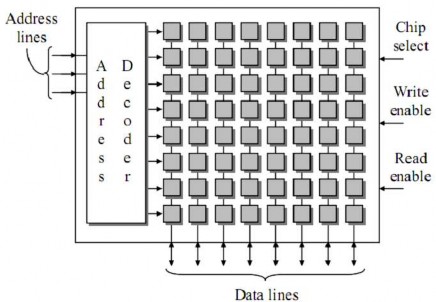

Để loại bỏ transistor chọn người ta dùng transistor SAMOS (Stacked Gate Avalanche Injection MOS) có cấu tạo tương tự transistor MOS nhưng có đến 2 cổng nằm chồng lên nhau, một được nối ra cực Gate và một để nổi. Khi cổng nổi tích điện sẽ làm gia tăng điện thế thềm khiến transistor trở nên khó dẫn điện hơn. Như vậy nếu ta chọn điện thế Vc ở khoảng giữa VT1 và VT2 là 2 giá trị điện thế thềm tương ứng với 2 trạng thái của transistor (VT1 Để xóa EPROM, người ta chiếu tia U.V. vào các tế bào trong một khoảng thời gian xác định để electron trên cổng nổi nhận đủ năng lượng vượt qua lớp cách điện trở về vùng nền tái hợp với lỗ trống xóa điện lộ P và transistor trở về trạng thái không dẫn ban đầu. Hình 4. 15. Xóa EPROM Điểm bất tiện của U.V EPROM là cần thiết bị xóa đặc biệt phát tia U.V. và mỗi lần xóa tất cả tế bào nhớ trong một IC nhớ đều bị xóa. Như vậy người sử dụng phải nạp lại toàn bộ chương trình Có thể bạn quan tâm! Xem toàn bộ 233 trang tài liệu này. Hình 4. 16. Hình dạng bên ngoài củaEPROM 4.3.2.3. EAROM EAROM (Electrically Alterable Rom) hay còn gọi là EEROM (Electrically Erasablr ROM) có cấu tạo tương tự EPROM nhưng có thể xóa được bằng xung điện. Đây là loại ROM lập trình được và xóa được nhờ xung điện và đặc biệt là có thể xóa để sửa trên từng byte. Các tế bào nhớ EEPROM sử dụng transistor MNOS (Metal Nitride Oxide Semiconductor) có cấu tạo như hình sau: Hình 4. 17. Cấu tạo EAPROM Giữa lớp kim loại nối ra các cực và lớp SiO2 là một lớp mỏng chất Nitrua Silic (Si3N4) - từ 40nm đến 650nm - Dữ liệu được nạp bằng cách áp một điện thế dương giữa cực G và S (khoảng 20 đến 25V trong 100ms). Do sự khác biệt về độ dẫn điện, electron tích trên bề mặt giữa 2 lớp SiO2 và Si3N4, các electron này tồn tại khi đã ngắt nguồn và làm thay đổi trạng thái dẫn điện của transistor. Bây giờ nếu áp một điện thế âm giữa cực G và S ta sẽ được một lớp điện tích trái dấu với trường hợp trước. Như vậy hai trạng thái khác nhau của Transistor có thể thiêt lập được bởi hai điện thế ngược chiều nhau và như vậy các tế bào nhớ được ghi và xóa với 2 xung điện trái dấu nhau. Loại EAROM ER 3400 của hãng General Instruments có dung lượng 1024*4 có thể giữ nội dung nhớ đến 10 năm, không cần nguồn nuôi. Thời gian ghi là 1ms, thời gian xóa là 10ms và thời gian đọc là 900ns. Một nhược điểm của mạch EAROM là cần các mức điện áp nguồn nuôi khác nhau trong khi xóa, ghi và đọc. Ví dụ mạch ER3400 cần 3 mức điện áp nuôi là: +12V, -5V và -30V. Hình 4. 18. Hình dạng và vị trí EEPROM trên bo mạch 4.3.3. Tổ chức bộ nhớ - Trước hết, chúng ta xem xét tổ chức của một ô nhớ. §iÒu khiÓn §iÒu khiÓn Chän D÷ liÖu vµo Chän D÷ liÖu ra ¤ nhí ¤ nhí a) Ghi b) §äc Hình 4. 19. Tổ chức ô nhớ Để đơn giản, ở đây chúng ta coi ô nhớ là phần tử nhớ được 1 bit thông tin. Khi muốn truy xuất dữ liệu từ ô nhớ thì bộ nhớ cần gửi các tín hiệu sau đến bộ nhớ: + Tín hiệu chọn (Chip select) được gửi đến để chọn ô nhớ + Tín hiệu điều khiển chỉ thị việc ghi hay đọc (Write enable/ Read enable) Sau đó, dữ liệu sẽ được đưa lên đường dữ liệu (Data lines) - Tổ chức mạch nhớ Hình 4. 20. Tổ chức mạch nhớ + Address lines: Các đường địa chỉ nối tới bus A, Truyền tín hiệu địa chỉ từ CPU tới mạch nhớ Address decoder: Bộ giải mã địa chỉ Sử dụng địa chỉ để chọn ra và kích hoạt ô nhớ/dòng nhớ cần truy nhập + Data lines: Các đường dữ liệu kết nối với bus D Truyền dữ liệu từ bộ nhớ về CPU và ngược lại Chip select CS: Chân tín hiệu chọn chip Chip nhớ được kích hoạt khi CS=0. Thông thường CPU chỉ làm việc với một chip nhớ tại một thời điểm. + Write enable WE: Chân tín hiệu cho phép ghi Cho phép ghi vào đường nhớ khi WE =0 + Read enable RE: Chân tín hiệu cho phép đọc Cho phép đọc dữ liệu từ đường nhớ khi RE =0 Chúng ta sẽ xem xét một mạch nhớ (chip nhớ) có sơ đồ như hình 4.21 sau đây: Bộ nhớ có 8 đường dây tín hiệu vào và 3 đường dây tín hiệu ra. Ba đường vào cho dữ liệu là • Tín hiệu chọn chip CS: Bộ nhớ của máy tính có thể bao gồm nhiều chip như trên, để chọn chip nhớ nào, mạch logic bên ngoài phải đặt cho đầu tín hiệu CS của chip đó có mức=1 và RD=1 để đọc hoặc RD=0 để ghi. • Tín hiệu địa chỉ: Hai đường dây địa chỉ phải được thiết lập giá trị để chỉ ra 1 trong 4 từ 3 bit sẽ được đọc hoặc ghi. Đối với thao tác đọc, các đường dây dữ liệu vào không được dùng đến, từ được chọn được đặt lên các đường dây dữ liệu ra. Đối với thao tác ghi, các bit có mặt trên đường dây dữ liệu vào được nạp vào từu bộ nhớ đã chọn, còn các đường dây dưc liệu ra không được sử dụng. Hình 4. 21. Sơ đồ logic chip nhớ 4x3, mỗi hàng là 1 từ nhớ 3 bit Bốn cổng AND cùng với 4 cổng NOT (mà các đầu váo nối với các dây địa chỉ - Ghi dữ liệu Khi chip nhớ được chọn để ghi, đường dây được ghi nhãn - Đọc dữ liệu Việc đọc cũng tương tự như việc ghi. Việc giải mã địa chỉ để ghi và đọc hoàn toàn giống nhau. Điểm khác nhau là tín hiệu của 3 cổng AND mà mỗi cổng có một đầu vào nối với nó có giá trị bằng các giá trị tại đầu ra Q của 3 flip-flop. Như vậy một từ đã đưa được nội dung ra. Mỗi bit dữ liệu của từ này được truyền tới một đầu vào trong số 4 đầu vào của một cổng OR ở phía dưới của hình vẽ. Ba đầu vào còn lại của mỗi cổng OR đều có giá trị 0, vì vậy giá trị của các cổng OR chính là từ mà chúng ta cần đọc. Phương pháp giải mã - Giải mã một bước Để lựa chọn một từ nằm trong hàng i nào đó của bộ nhớ trên (để ghi hoặc đề đọc) ta cần đặt các dây địa chỉ một giá trị địa chỉ n bit chính bằng i. Bộ giải mã địa chỉ chỉ cần một bước là thực hiện được việc chọn lấy 1 từ. Phương pháp tổ chức bộ nhớ trong đó tất cả các phần tử nhớ trên một hàng được gắn với một địa chỉ và được thao tác đọc/ghi đồng thời được gọi là tổ chức bộ nhớ theo kiểu giải mã một bước hoặc tổ chức bộ nhớ theo từ sự chọn tuyến tính. Ưu điểm: có thời gian truy cập ngắn , áp dụng thuận lợi cho các bộ nhớ có dung lượng nhỏ. Nhược điểm: khi dung lượng bộ nhớ lớn thì kích thước bộ giải mã (số chân ra) cũng tăng theo. Thí dụ nếu cần tổ chức bộ nhớ có 1024 từ thì bộ giải mã cần có 10 đường địa chỉ vào và sẽ có 1024 đầu ra để chọn hàng. Các bộ nhớ SRAM thường tổ chức theo phương pháp này. Hình 4. 22. Giải mã 1 bước - Giải mã hai bước Kích thước của bộ giải mã địa chỉ có thể được giảm đi bằng cách tổ chức ma trận nhớ hoặc logic chọn từ cho phép chọn trùng hợp (coincident selection) hay còn gọi là giải mã hai bước. Trong bộ nhớ tổ chức theo kiểu này, các ô nhớ được sắp xếp thành ma trận vuông, các bit trên một hàng được gọi là một từ vật lý, mỗi từ vật lý bao gồm một số từ logic, mỗi từ logic bao gồm một nhóm bit của mỗi từ vật lý được nhận biết và gửi ra cùng một lúc. Trong bộ nhớ sử dụng giải mã 2 bước, bước một để chọn lấy một từ vật lý, bước hai để chọn lấy một từ logic. Bộ giải mã hàng để chọn lấy một từ vật lý và bộ giải mã cột gồm một vài bộ dồn kênh, chọn lấy một từ logic trong từ vật lý đã chọn. Hình 4.23 là một bộ nhớ ROM 2048x8 (2048 từ x 8bit/1 từ). Bộ nhớ này là một ma trận vuông 128x128. Như vậy, nó chứa 128 từ vật lý, mỗi từ vật lý được chọn bởi 7 đường địa chỉ hàng A0 – A6 (27 = 128), bộ giải mã hàng chọn 1 hàng từ 128 hàng. Từ vật lý được chia làm 8 nhóm 16 bit. Nhóm thứ nhất chứa bít cao nhất của 16 từ logic (bit 7), nhóm thứ hai chứa những bit cao tiếp theo (bit 6) của 16 từ logic,... Nhóm cuối cùng chứa những bit thấp nhất (bit 0) của 16 từ logic. Như vậy các bộ giải mã cột gồm 8 bộ dồn kênh (multiplexer) 16 đường vào 1 đường ra để cung cấp 1 từ logic 8 bit đưa ra lối ra. Các bit địa chỉ A7, A8, A0, A10 điều khiển những bộ giải mã cột. Hình 4. 23. Bộ nhớ ROM 2048x8 - Giải mã địa chỉ 2 bước - Phương pháp địa chỉ multiplex Trong các ma trận nhớ có số hàng và số cột lớn người ta thường truyền lần lượt địa chỉ hàng và địa chỉ cột trên cùng một số dây, nhờ đó giảm được một nửa số đường địa chỉ. Tuy nhiên cần phải bổ sung thêm một số tín hiệu điều khiển, ngoài ra tốc độ truy cập bộ nhớ cũng giảm theo. Đó là phương pháp địa chỉ multiplex, các chip nhớ DRAM thường dùng phương pháp này. Dùng n đường địa chỉ dồn kênh cho phép truyền 2n bit địa chỉ Tín hiệu chọn địa chỉ hàng RAS (Row Address Select) Tín hiệu chọn địa chỉ cột CAS (Column Address Select) Dung lượng của DRAM: 22n x m bit Hình 4. 24. Chip nhớ 16MB DRAM (4Mx4bit) Hình 4. 25. Hình ảnh các chip nhớ trên bo mạch

Kiến trúc máy tính - 15

Kiến trúc máy tính - 15 Bộ Nhớ Và Các Hệ Thống Lưu Trữ

Bộ Nhớ Và Các Hệ Thống Lưu Trữ Prom – Rom Có Thể Nạp Chương Trình

Prom – Rom Có Thể Nạp Chương Trình Kiến trúc máy tính - 19

Kiến trúc máy tính - 19 Các Phương Pháp Ánh Xạ Giữa Cache Và Bộ Nhớ Chính

Các Phương Pháp Ánh Xạ Giữa Cache Và Bộ Nhớ Chính Kiến trúc máy tính - 21

Kiến trúc máy tính - 21

![]() ,

, ![]() ,

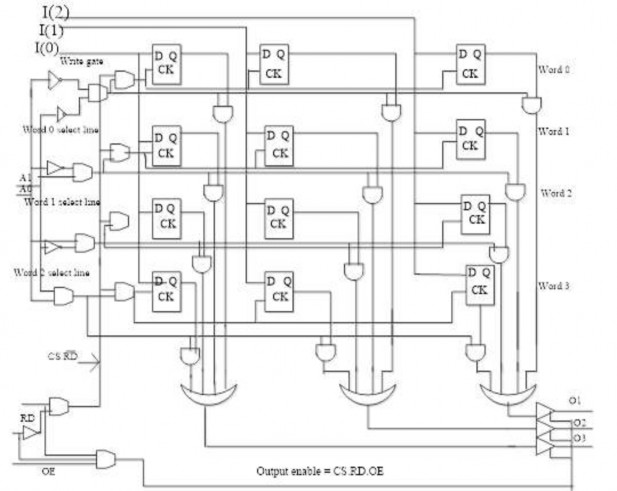

, ![]() ; hai đường vào địa chỉ là

; hai đường vào địa chỉ là ![]() ,

, ![]() và 3 đường tín hiệu điều khiển là CS (Chip select) để chọn chip, RD để phân biệt giữa đọc (read) và ghi (write) và OE (Output enable) để đưa dữ liệu ra. Ba đường ra cho dữ liệu là

và 3 đường tín hiệu điều khiển là CS (Chip select) để chọn chip, RD để phân biệt giữa đọc (read) và ghi (write) và OE (Output enable) để đưa dữ liệu ra. Ba đường ra cho dữ liệu là ![]() ,

, ![]() và

và ![]() .

.

![]() ,

, ![]() ) tạo thành 1 bộ giải mã dùng để chọn từ, mỗi đầu ra của 1 cổng AND điều khiển 1 dây chọn từ (word select line), được đánh số 0…3.

) tạo thành 1 bộ giải mã dùng để chọn từ, mỗi đầu ra của 1 cổng AND điều khiển 1 dây chọn từ (word select line), được đánh số 0…3.![]() sẽ có mức cao, làm cho đầu ra của 1 trong 4 cổng AND có nhãn Write gate ở mức tích cực, đó là cổng AND có 1 đầu vào nối với dây word select có mức cao. Tín hiệu này nối với tất cả các đầu vào CK của từ đã được chọn, làm cho dữ liệu trên các dây dữ liệu vào

sẽ có mức cao, làm cho đầu ra của 1 trong 4 cổng AND có nhãn Write gate ở mức tích cực, đó là cổng AND có 1 đầu vào nối với dây word select có mức cao. Tín hiệu này nối với tất cả các đầu vào CK của từ đã được chọn, làm cho dữ liệu trên các dây dữ liệu vào ![]() ,

, ![]() ,

, ![]() nạp vào các flip-flop của từ đó.

nạp vào các flip-flop của từ đó.![]() phải có mức thấp, vì vậy các cổng AND có nhãn Write gate đều có lối ra ở mức thấp, làm cho tín hiệu ở các chân CK của các flip-flop có mức thấp, do đó các flip-flop không thể thay đổi trạng thái. Một trong bốn đường dây chọn từ (word select line) có mức cao, làm cho tại 3 đầu ra

phải có mức thấp, vì vậy các cổng AND có nhãn Write gate đều có lối ra ở mức thấp, làm cho tín hiệu ở các chân CK của các flip-flop có mức thấp, do đó các flip-flop không thể thay đổi trạng thái. Một trong bốn đường dây chọn từ (word select line) có mức cao, làm cho tại 3 đầu ra