Giá trị thực tế của β thay đổi theo bóng bán dẫn. Nó thường khoảng 100, nhưng có thể nằm trong khoảng từ 50 đến 200… thậm chí 2000, tùy thuộc vào loại Transistorbạn đang sử dụng và lượng hiện tại đang chạy qua nó. Ví dụ, nếu transistor của bạn có β 100, nghĩa là dòng đầu vào 1mA vào đế có thể tạo ra dòng điện 100mA qua bộ thu.

α thường nhỏ hơn, 1. Điều đó có nghĩa là IC rất gần, nhưng ít hơn IE ở chế độ hoạt động.

Bạn có thể sử dụng β để tính α hoặc ngược lại:

= /1-

= / +1

Có thể bạn quan tâm!

-

Hình Ảnh Các Transistor Tín Hiệu Nhỏ Transistor Công Suất (Power Transistors)

Hình Ảnh Các Transistor Tín Hiệu Nhỏ Transistor Công Suất (Power Transistors) -

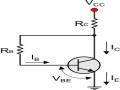

Phân Cực Hồi Tiếp Thu (Collector Feedback Biasing)

Phân Cực Hồi Tiếp Thu (Collector Feedback Biasing) -

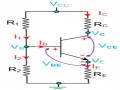

Phân Cực Hồi Tiếp Kép (Dual Feedback Transistor Biasing)

Phân Cực Hồi Tiếp Kép (Dual Feedback Transistor Biasing) -

Sơ Đồ Biểu Diễn 3 Chế Độ Hoạt Động Của Jfet

Sơ Đồ Biểu Diễn 3 Chế Độ Hoạt Động Của Jfet -

Linh Kiện Có Vùng Điện Trở Âm

Linh Kiện Có Vùng Điện Trở Âm -

Mạch Điều Khiển Động Cơ Dùng Scr

Mạch Điều Khiển Động Cơ Dùng Scr

Xem toàn bộ 264 trang tài liệu này.

Ví dụ, nếu β là 100, nghĩa là α là 0,99. Vì vậy, nếu IC là 100mA, ví dụ, sau đó IE là 101mA.

Đảo ngược hoạt động

Cũng như bão hòa là đối diện của cutoff, ngược lại chế độ hoạt động là đối diện của chế độ hoạt động. Một Transistortrong chế độ hoạt động đảo ngược tiến hành, thậm chí khuếch đại, nhưng dòng chảy theo hướng ngược lại, từ emitter để thu. Nhược điểm để đảo ngược chế độ hoạt động là β (βR trong trường hợp này) là nhỏ hơn nhiều.

VC < VB< VE

Để đặt một Transistorở chế độ hoạt động đảo ngược, điện áp phát ra phải lớn hơn đế, phải lớn hơn bộ thu (VBE <0 và VBC> 0).

CÂU HỎI ÔN TẬP

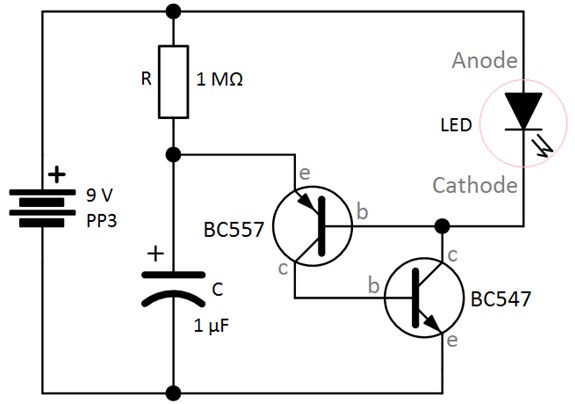

Câu 1: Trình bày ký hiệu của BJT loại NPN và PNP Câu 2: Nêu các tính chất của các cực E,B,C của BJT Câu 3: Giải thích NLHĐ của mạch ứng dụng sau

Câu 4: Vẽ mạch tự phân cực của Transisror

Câu 5: Thiết lập các biểu thức dòng áp mạch hồi tiếp Câu 6: Trình bày mạch mắc kiểu B chung

Câu 7: Trình bày mạch mắc kiểu C chung Câu 8: Trình bày mạch mắc kiểu E chung

Chương 5: TRANSITOR HIỆU ỨNG TRƯỜNG (FET)

1. Mục tiêu

+ Trình bày cấu tạo của transitor hiệu ứng trường

+ Phân biệt được ký hiệu các loại transitor hiệu ứng trường.

+ Phân tích được nguyên lý vận chuyển của các loại JFET, MOSFET.

+ Phân tích sự phân cực của JFET, MOSFET

+ Vận dụng FET vào trong mạch nguồn, mạch khuếch đại…

2. Nội dung chính

1.1 Khái niệm

1.2 JFET

2.2.1 Cấu tạo – ký hiệu

2.2.2 Nguyên lý vận chuyển

2.2.3 Đặc tuyến – phân cực

1.3 MOSFET

2.3.1 MOSFET kênh liên tục

2.3.2 MOSFET kênh gián đoạn

5.1. Khái niệm

FET lần đầu tiên được cấp bằng sáng chế cho Julius Edgar Lilienfeld vào năm 1926 và cho Oskar Heil vào năm 1934, Trong khi đó JFET được William Shockley phát triển tại Bell Labs vào năm 1947.

Loại đầu tiên của JFET là transistor cảm ứng tĩnh SIT (static induction transistor), được phát minh bởi các kỹ sư người Nhật Bản là Jun-ichi Nishizawa và Y. Watanabe vào năm 1950. SIT là một loại JFET với độ dài kênh ngắn. Sau đó MOSFET phần lớn dùng để thay thế cho JFET và nó có ảnh hưởng sâu sắc đến phát triển điện tử kỹ thuật số, được phát minh bởi Dawon Kahng và Martin Atalla vào năm 1959.

FET là cụm từ viết tắt của Field-Effect Transistor, đây là transistor hiệu ứng trường. FET cũng được biết đến như là Transistor đơn cực (unipolar transistors) vì nó liên quan đến hoạt động của một loại hạt dẫn: hạt dẫn điện tử (electrons) kênh N hoặc lỗ trống (holes) kênh P

FET có trở kháng vào rất lớn (hàng ngàn Ohms) ở tần số thấp. Độ dẫn điện giữa cực máng (Drain) và nguồn (Source) được điều khiển bởi điện trường do sự chênh lệch điện áp giữa thân (Body) và cổng (Gate) của thiết bị. Điều này làm cho transistor hiệu ứng trường là một thiết bị vận hành theo điện áp (Voltage). FET sử dụng điện áp được cấp cho cực Gate để điều khiển dòng điện chạy qua chúng, khiến cho dòng điện đầu ra tỷ lệ thuận với điện áp đầu vào.

Có hai loại transistor hiệu ứng trường chính đó là JFET (Transistor Field Effect Transistor ) và IGFET (Transistor Field Effect Transistor) thường được gọi là MOSFET (Metal Oxide Semiconductor Field Effect Transistor).

FET là thiết bị có 3 đầu cuối (three terminals) tướng ứng 3 chân:

Chân nguồn (S): các hạt mang điện truyền vào kênh. Thông thường, dòng vào tại kênh S được đặt là IS.

Chân máng (D), thông qua đó các hạt mang điện rời khỏi kênh. Dòng vào kênh D được gọi là ID. Điện áp từ D tới S gọi là VDS.

Chân cổng (G), điều chỉnh độ dẫn kênh, nghĩa là cho phép các electron chảy qua hoặc chặn dòng của chúng bằng cách tạo ra hoặc loại bỏ một kênh giữa nguồn và máng. Khi cấp điện áp cho G, người ta có thể kiểm soát được dòng ID.

Hầu hết các FET còn có một thiết bị đầu cuối thứ tư (fourth terminal) được gọi là thân (Body) hay nền, đế (Substrate / Base). Thiết bị đầu cuối thứ tư này dùng để phân cực cho transistor hoạt động và nó rất quan trọng khi thiết lập bố trí vật lý của mạch tích hợp.

5.2. JFET

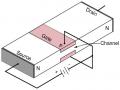

5.2.1 Cấu tạo – ký hiệu

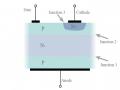

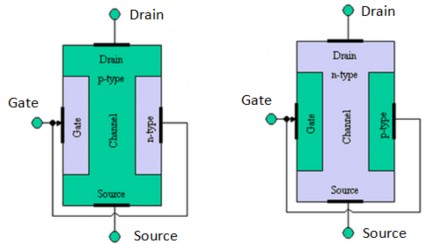

JFET bao gồm một thanh silicon loại P hoặc N chứa hai mối nối P - Nở hai bên thanh. Khi đó thanh trở thành kênh dẫn các hạt mang điện.

Nếu thanh là loại P, nó được gọi là JFET kênh P và nếu thanh là loại N, nó được gọi là JFET kênh N.

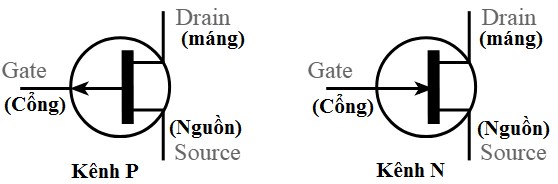

Hình 5.1: Cấu tạo của JFET

JFET kênh N có độ dẫn kênh lớn hơn (điện trở thấp hơn) so với các JFET kênh P tương đương của chúng, vì các electron có tính di động cao hơn so với các lỗ trống.

Hai mối nối P - Nhình thành Diode tạo kết nối bên trong và một đầu chung được lấy ra gọi là chân cổng G (Gate).

Hai chân khác là chân nguồn S (Source) và chân máng D (Drain) được xuất ra từ 2 đầu của thanh.

Vì vậy, một JFET có ba thiết bị đầu cuối: cổng (G), nguồn (S) và máng (D).

Hình 4.2: Ký hiệu JFET kênh P và N

5.2.2 Nguyên lý vận chuyển

Hoạt động của kênh FET N (Operation of N-channel FET)

JFET là thiết bị điều khiển điện áp. Nói cách khác, điện áp xuất hiện trên cổng (G), kiểm soát hoạt động của thiết bị.

Cả hai thiết bị kênh N và kênh P đều hoạt động theo các cách tương tự, nhưng chiều dòng điện ngược lại. Trường hợp JFET kênh N sẽ được mô tả vì đây là loại thường được sử dụng hơn.

Độ dày của lớp này thay đổi theo độ lớn phân cực nghich của mối nối:

Khi phân cực ngược nhỏ, lớp cạn kiệt chỉ mở một kênh nhỏ để dòng điện chạy qua.

Khi phân cực nghịch lớn được đặt trên cổng, lớp suy giảm tăng lên, kênh càng bị thu hẹp, dòng điện di qua giảm.

Khi phân cực nghịch càng tăng, lớp suy giảm sẽ tăng lên mức độ mà kênh dẫn bị bịt kín nên ngăn cản không cho dòng điện đi qua

Độ lớn của dòng điện chạy qua kênh phụ thuộc vào một số yếu tố như diện tích mặt cắt ngang của kênh, chiều dài và độ dẫn của kênh (tức là số lượng electron tự do trong vật liệu) và điện áp phân cực.

Hoạt động của JFET có thể được giải thích như sau:

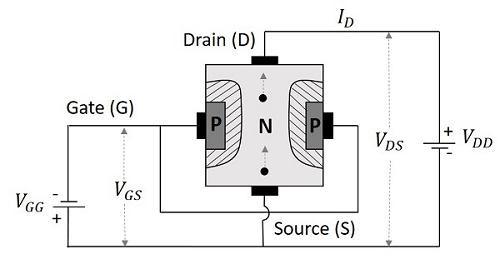

Khi một điện áp VDS được áp giữa D và S và điện áp trên G bằng 0, hai mối nối PN ở hai bên của thanh thiết lập các lớp suy giảm.

Trong trường hợp 1, khi VGG phân cực nghịch và VDD không được đặt vào, các vùng suy giảm giữa các lớp P và N có xu hướng mở rộng. Điều này xảy ra khi điện áp âm áp dụng, thu hút các lỗ từ lớp loại P về phía cổng G.

Trong trường hợp 2, khi VDD được áp (Cực dương tại D và cực âm tại S) và VGG không được cấp, các electron chảy từ nguồn S đến máng D tạo thành dòng xả ID

Hình 5.3: Phân cực kênh dẫn cho JFET

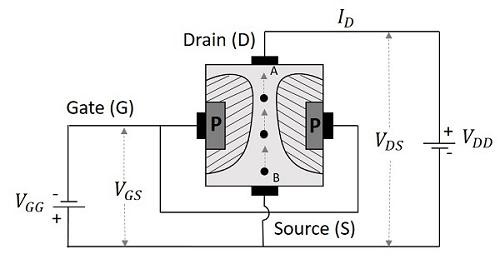

Do độ giảm điện áp thông qua chiều dài của kênh. Vì vậy, hiệu ứng phân cực ngược tại G mạnh hơn tại S. Nên lớp suy giảm có xu hướng thâm nhập nhiều hơn vào kênh tại điểm A so với điểm B, khi cấp nguồn VGG và VDD

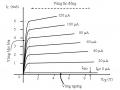

Hình 5.4: Chế độ hoạt động của JFET

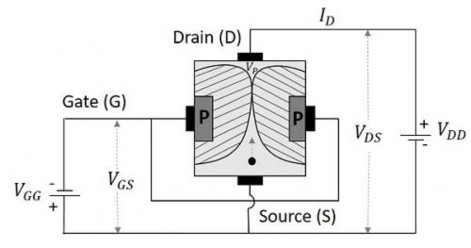

Chế độ hoạt động cạn kiệt (Depletion Mode of Operation)

Do chiều rộng của lớp cạn kiệt đóng một vai trò quan trọng trong hoạt động của FET, nhưng JFET chỉ có chế độ hoạt động cạn kiệt.

Khi cả hai lớp cạn kiệt chạm vào nhau và ngăn dòng chảy ID hiện tại. Điều này được thể hiện rõ trong hình dưới đây.

Hình 5.5 : Phân cực ngưng dẫn cho JFET