Bit 3 ADDEN : bit cho phép phat hiện địa chỉ. Chế độ bất đồng bộ 9 bit (RX9 = 1):

+ 1 = cho phép phat hiện địa chỉ, cho phép nhắt và tải bộ đệm nhận khi RSR<8> được SET.

+ 0 = không cho phép phát hiện địa chỉ, tất cả các Bytes được nhận và bit thứ 9 có thể được sử dụng như là bit Parity.

Bit 2 FERR : bit báo lỗi khung truyền

+ 1 = lỗi khung truyền (có thể được chấp nhận bằng cách đọc thanh ghi RCREG và nhận Byte tiếp theo).

+ 0 = không xuất hiện lỗi trong quá trình truyền nhận dữ liệu.

Bit 1 OERR : bit báo lỗi tràn bộ nhớ.

+ 1 = lỗi tràn ( có thể xóa bằng cách xóa bit CREN).

+ 0 = không báo lỗi tràn.

Bit 0 RX9D : bit thứ 9 của dữ liệu nhận ( có thể là bit parity nhưng phải được tính toán bởi người dùng).

Có thể bạn quan tâm!

-

Các Thành Phần Của Hệ Thống Thông Tin Di Động Gsm

Các Thành Phần Của Hệ Thống Thông Tin Di Động Gsm -

Chu Kỳ Xung Clock Và Tần Số Làm Việc Của Adc

Chu Kỳ Xung Clock Và Tần Số Làm Việc Của Adc -

Sơ Đồ Khối Bộ Truyền Dữ Liệu Eusart Bất Đồng Bộ

Sơ Đồ Khối Bộ Truyền Dữ Liệu Eusart Bất Đồng Bộ -

Khảo Sát Sơ Đồ Chân Và Chức Năng Từng Chân

Khảo Sát Sơ Đồ Chân Và Chức Năng Từng Chân -

Sơ Đồ Mạch Led Thu Với Bộ So Sánh Tương Đương

Sơ Đồ Mạch Led Thu Với Bộ So Sánh Tương Đương -

Hệ Thống Được Cấp Nguồn Và Sẵng Sàng Hoạt Động

Hệ Thống Được Cấp Nguồn Và Sẵng Sàng Hoạt Động

Xem toàn bộ 104 trang tài liệu này.

2.6.2 Bộ EUSART hoạt động trong chế độ đồng bộ

Giao diện EUSART đồng bộ được kích hoạt bằng cách set bit SYNC. Cổng giao tiếp nối tiếp vẫn là hai chân RC7/RX/DT, RC6/TX/CK và được cho phép bằng cách set bit SPEN. EUART cho phép hai chế độ truyền nhận dữ liệu là Master mode và Slave mode. Master mode được kích hoạt bằng cách set bit CSRC (TXSTA<7>), Slave mode được kích hoạt bằng cách Clear bit CSRC. Điểm khác biệt duy nhất giữa hai chế độ này làMaster mode sẽ lấy xung clock đồng bộ từ bộ tạo xung baud BRG còn Slave mode lấy xung clock đồng bộ từ bên ngoài qua chân RC6/TX/CK. Điều này cho phép Slave mode hoạt động ngay cả khi vi điều khiển đang ở chế độ sleep.

2.7 HOẠT ĐỘNG ĐỊNH THỜI TIMER

2.7.1 Bộ định thời TIMER0

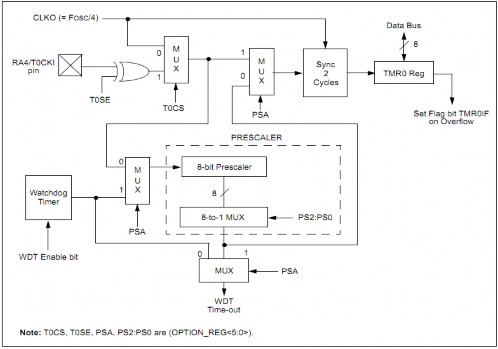

Bộ định thời/bộ đếm Timer0 có các đặc tính sau :

- Bộ định thời / bộ đếm 8 bit .

- Cho phép đọc và ghi .

- Bộ chia 8 bit lập trình được bằng phần mềm .

- Chọn xung clock nội hoặc ngoại .

- Ngắt khi có sự tràn từ FFh đến 00h

- Chọn cạnh cho xung clock ngoài

Bên dưới là sơ đồ khối của bộ định thời Timer 0 và bộ chia dùng chung với WDT. Chế độ định thời (Timer) được chọn bằng cách xóa bit T0CS ( OPTION_REG<5> ) Trong chế độ định thời , bộ định thời Timer 0 sẽ tăng dần sau mỗi chu kỳ lệnh ( không có bộ chia ) . Nếu thanh ghi TMR0 được ghi thì sự tăng sẽ bị ngăn lại sau hai chu kỳ lệnh .

Chế độ đếm(Counter) được chọn bằng cách set bit T0SC ( OPTION_REG<5> ). Trong chế độ đếm , Timer0 sẽ tăng dần ở mỗi cạnh lên hoặc cạnh xuống của chân RA4/T0CKI . Sự tăng cạnh được xác định bởi bit Timer0 Source Edge Select , T0SE (OPTION_REG<4> ) . Bộ chia chỉ được dùng chung qua lại giữa bộ định thời Timer0 và bộ định thời Watchdog . Bộ chia không cho phép đọc hoặc ghi .

Ngắt TMR0 được phát ra khi thanh ghi TMR0 tràn từ FFh đến 00h đối với 8 bit. Sự tràn này sẽ set bit TMR0IF(INTCON<2>). Ngắt này có thể được giấu đi bằng cách xóa đi bit TMR0IE (INTCON<5>) . Bit TMR0IF cần phải được xóa trong chương trình bởi thủ tục phục vụ ngắt của bộ định thời Timer0 trước khi ngắt này được cho phép lại.

Sơ đồ khối của Timer 0 như sau:

Hình 2.18 sơ đồ khối bộ định thời Timer0

Muốn Tmer 0 hoạt động ở chế độ Timer ta clear bit T0SC (OPTION_REG<5>), khi đó giá trị thanh ghi TMR0 sẽ tăng theo từng chu kỳ xung đồng hồ (tần số vào

Timer 0 bằng 1/4 tần số oscillator). Khi giá trị thanh ghi TMR0 từ FFh trở về 00h, ngắt Timer 0 sẽ xuất hiện.

Thanh ghi TMR0 cho phép ghi va xoa được giúp ta ấn định thời điểm ngắt Timer 0 xuất hiện một cách linh động . Muốn Timer 0 hoạt đọng o chế độ counter ta set bit T0CS (OPTION_REG<5>). Khi đó xung tác động lên bộ đếm được lấy từ chân RA4/T0CKI. Bit T0SE (OPTIN_REG<4>) cho phép lựa chọn cạnh tác động vào bộ đếm. Cạnh tác động sẽ là cạnh lên nếu T0SE = 0 và cạnh tác động sẽ là cạnh xuống nếu T0SE = 1.

Khi thanh ghi TMR0 bị tràn, bit TMR0IF (INTCON<2>) sẽ được set. Đây chính là cờ ngắt của Timer 0. Cờ ngắt này phải được xóa bằng chương trình trước khi bộ đếm bắt đầu thực hiện lại quá trình đếm .NGắt Timer 0 không thể đánh thức vi điều khiển từ chế độ sleep

Bộ chia tần số (prescaler) được chia sẻ giữa Timer 0 và WDT (Watchdog Timer). Điều đó có nghĩa là nếu bộ chia tần số được sử dụng cho timer 0 thì WDT sẽ không có hỗ trợ của bộ chia tần số và ngược lại. Bộ chia tần số được điềi khiển bởi thanh ghi OPTION_REG. Bit PSA (OPTION_REG<3>) xác định đối tượng tác động của bộ chia tần số. Các bit PS2:PS0 (OPTION_REG<2:0>) xác định tỉ số của bộ chia tần số. Các lệnh tác động lên giá trị thanh ghi TMR0 sẽ xóa chế độ hoạt động của bộ chia tần số.

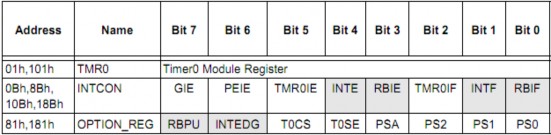

Các thanh ghi điều khiển liên quan đến Timer 0 bao gồm : TMR0 (địa chỉ 01h,101h) : chứa giá trị đếm của Timer 0. INTCON (địa chỉ 0Bh,8Bh,10Bh,18Bh)):cho phép ngắt hoạt . OPTION_REG (địa chỉ 81h,181h) : điều khiển bộ chia tần số.

Hình 2.19 Các thanh ghi liên quan đến bộ định thời Timer0

2.7.2 Bộ định thời TIMER1

Bộ định thời Timer1 là một bộ định thời/bộ đếm 16 bit gồm hai thanh ghi TMR1H ( byte cao ) và TMR1L ( byte thấp ) mà có thể đọc hoặc ghi . Cặp thanh ghi

này tăng số đếm từ 0000h đến FFFFh và một tràn sẽ xuất hiện khi có sự chuyển số đếm từ FFFFh xuống 0000h . Ngắt, nếu được phép có thể phát ra khi có số đếm tràn và được đặt ở bit cờ ngắt TMR1IF. Ngắt có thể được phép hoặc cấm bằng cách đặt hoặc xóa bit cho phép ngắt TMR1IE.

Bộ định thời Timer1 có thể được cấu hình để hoạt động một trong hai chế độ sau:

- Định thời một khoảng thời gian ( Timer )

- Đếm sự kiện ( Counter )

Việc lựa chọn một trong hai chế độ được xác định bằng cách đặt hoặc xóa bit chọn clock TMR1CS. Trong chế độ định một khoảng thời gian, bộ định thời tăng số đếm lên sau mỗi chu kỳ lệnh. Trong chế độ đếm sự kiện, bộ định thời tăng sau mỗi cạnh lên của clock ngoài đặt vào. Bộ định thời 1 có thể được phép hoặc cấm bằng cách đặt hoặc xóa bit điều khiển TMR1ON.

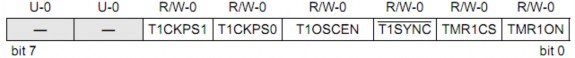

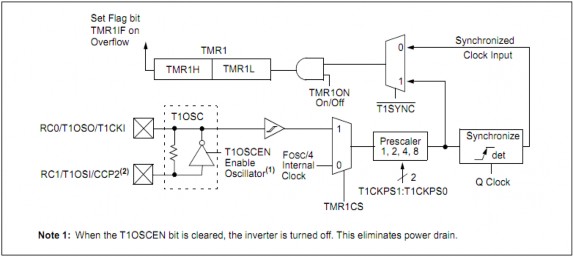

Hình 2.20 T1CON: Thanh ghi điều khiển Timer1

Hình 2.21 Sơ đồ khối Timer1

Ngoài ra Timer 1 còn có chức năng reset input bên trong được điều khiển bởi một trong hai khối CCP (Capture/Compare/PWM).Khi set bit T1OSCEN thì Timer 1 sẽ lấy xung clock từ hai chân RC/T1OSI/CCP2 và RC0/T1OSO/T1CKI làm xung đếm. Timer 1 sẽ bắt đầu đếm sau cạnh xuống đầu tiên của xung ngõ vào. Khi đó PORTC sẽ bỏ qua sự tác động của hai bit TRISC<1:0> và PORTC<2:1> được gán giá trị 0 . Khi

clear bit T1OSCEN Timer 1 sẽ lấy xung đếm từ oscillator hoặc từ chân RC0/T1OSO/T1CKI.

Timer 1 có hai chế độ đếm là đồng bộ (Synchronous) và bất đồng bộ (Asynchronous). Chế độ đếm được quyết định bởi bit điều khiển T1SYNC (T1CON<2>).

Khi T1SYNC = 1 xung đếm lấy từ bên ngoài sẽ không được đồng bọ hóa với xung clock bên trong, Timer 1 sẽ tiếp tục quá trình đếm vi điều khiển đang ở chế độ sleep và ngắt do Timer tạo ra khi bi tràn có khả năng đánh thức vi điều khiển. Ở chế độ đếm bất đòng bộ, Timer 1 không thể được sử dụng để làm nguồn xung clock cho khói CCP (Capture/Compare/Pulse width modulation).

Khi T1SYNC = 0 xung đếm vào Timer 1 sẽ được đồng bộ hóa với xung clock bên trong. Ở chế độ này Timer 1 sẽ không hoat động khi vi điều khiẻn đang ở chế độ sleep.

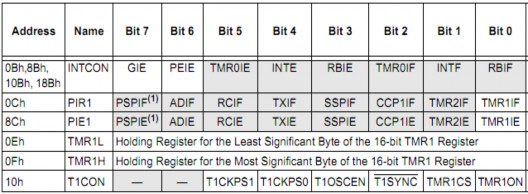

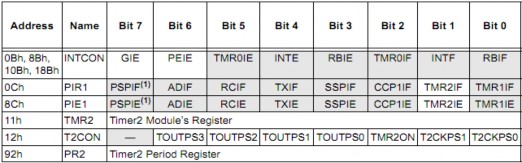

Các thanh ghi liên quan đến Timer 1 bao gồm:

INTCON (địa chỉ 0Bh, 8Bh,10Bh, 18Bh) : cho phép ngắt hoạt động. PIR1 (địa chỉ 0Ch): chứa cờ ngắt Timer 1 (TMR1IF).

PIE1 (địa chỉ 8Ch): cho phép ngắt Timer 1 (TMR1IE).

TMR1L (địa chỉ 0Eh): chứa giá trị 8 bít thấp của bộ đếm Timer 1. TMR1H (địa chỉ 0Fh): chứa giá trị 8 bít cao của bộ đếm Timer 1. T1CON (địa chỉ 10h): xác lập các thông số cho Timer 1.

Hình 2.22 Các thanh ghi liên quan đến bộ định thời Timer1

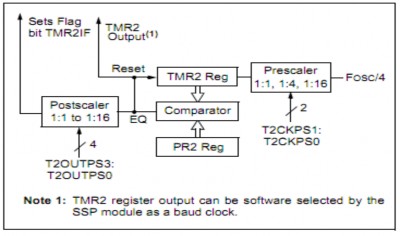

2.7.3 Bộ định thời TIMER2

Bộ định thời Timer2 là bộ định thời 8 bit với một bộ chia và một bộ Postscaler. Nó thường được dùng chung với bộ CCP trong chế độ PWM ( sẽ được đề cập ở phần

sau ). Thanh ghi TMR2 có thể đọc hoặc ghi và được xóa khi có bất kỳ tín hiệu reset nào của thiết bị.

Bộ định thời Timer2 có một thanh ghi chu kỳ 8 bit. Bộ định thời tăng số đếm lên từ 00h đến giá trị được ghi trong thanh ghi TR2 và sau đó reset lại giá trị 00h trong chu kỳ kế tiếp. PR2 là thanh ghi có thể đọc hoặc ghi.Giá trị trùng hợp trong thanh ghi TMR2 được đi qua bộ postscaler 4 bit để phát ra một ngắt TMR2(được đặt ở bit cờ ngắt TMR2IF). Bộ định thời 2 có thể được tắt ( không hoạt động ) bằng cách xóa bit điều khiển TMR2ON để giảm thiểu công suất tiêu tán nguồn.

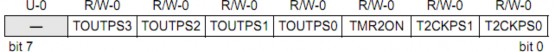

Hình 2.23 T2CON: Thanh ghi điều khiển Timer2

Hình 2.24 Sơ đồ khối của bộ định thời Timer2

Hình 2.25 Các thanh ghi liên quan đến bộ định thời Timer2

2.8 NGẮT (INTERRUPT)

PIC16F877A có nhiều nguồn tạo ra hoạt động ngắt và được điều khiển bởi rất nhiều thanh ghi: RCON; INTCON; INTCON2; INTCON3; PIR1, PIR2; PIE1, PIE2;

IPR1, IPR2. Bên cạnh đó mỗi ngắt còn có một bit điều khiển và cờ ngắt riêng. Các cờ ngắt vẫn được set bình thường khi thỏa mãn điều kiện ngắt xảy ra bất chấp trạng thái của bit GIE, tuy nhiên hoạt động ngắt vẫn phụ thuộc vào bit GIE và các bit điều khiển khác. Bit điều khiển ngắt RB0/INT0 và TMR0 nằm trong thanh ghi INTCON, thanh ghi này còn chứa bit cho phép các ngắt ngoại vi PEIE. Bit điều khiển các ngắt nằm trong thanh ghi PIE1 và PIE2. Các cờ ngắt ngoại vi được chứa trong hai thanh ghi chức năng đặc biệt : thanh ghi PIR1 và PIR2.Các bit cho phép ngắt tương ứng được chứa trong hai thanh ghi PIE 1 và PIE 2.

Trong một thời điểm chỉ có một chương trình ngắt được thực thi, chương trình ngắt được kết thúc bằng lệnh RETFIE. Khi chương trình ngắt được thực thi, bit GIE tự động được xóa, địa chỉ lệnh tiếp theo của chương trình chính được cất vào trong bộ nhớ Stack và bộ đếm chương trình sẽ chỉ đến địa chỉ 0008h. Lệnh RETFIE được dùng để thoát khỏi chương trình ngắt và quay trở về chương trình chính, đồng thời bit GIE cũng sẽ được set để cho phép các ngắt hoạt động trở lại. Các cờ hiệu được dùng để kiểm tra ngắt nào đang xảy ra và phải được xóa bằng chương trình trước khi cho phép ngắt tiếp tục hoạt động trở lại để ta có thể phát hiện được thời điểm tiếp theo mà ngắt xảy ra.

Khi một ngắt được đáp ứng, bit GIE được xóa và cấm tất cả các ngắt khác.Cờ ngắt phải được xóa bởi phần mềm trước khi cho phép lại ngắt.Thông thường, trước khi thực hiện các chương trình phục vụ ngắt, nội dung các thanh ghi w và status nên được lưu lại để bảo đảm an toàn và được phục hồi trước khi trở lại chương trình chính.

Đối với các ngắt ngoại vi như ngắt từ chân INT hay ngắt từ sự thay đổi trạng thái các Pin của PortB (PORTB interrupt-on-change), việc xác định ngắt nào xảy ra cần 3 hoặc 4 chu kì lệnh tùy thuộc vào thời điểm xảy ra ngắt.

Trong quá trình thực thi ngắt, chỉ có giá trị của bộ đếm chương trình được cất vào trong Stack, trong khi một số thanh ghi quan trọng sẽ không được cất và có thể bị thay đổi giá trị trong quá trình thực thi chương trình ngắt. Điều này nên được xử lí bằng chương trình để tránh hiện tượng trên xảy ra.

CHƯƠNG 3. THIẾT KẾ VÀ XÂY DỰNG HỆ THỐNG CẢM BIẾN VÀ PHÁT CẢNH BÁO MỰC NƯỚC, NHIỆT ĐỘ QUA MẠNG TIN NHẮN SMS

3.1 GIỚI THIỆU MODULE SIM900, TẬP LỆNH AT COMMAND.

3.1.1 Giới thiệu module SIM900

Các modem được sử dụng từ những ngày đầu của sự ra đời máy tính. Từ Modem là một từ được hình thành từ hai từ modulator và demodulator. Và định nghĩa đặc trưng này cũng giúp ta hình dung được phần nào là thiết bị này sẽ làm cái gì. Dữ liệu số thì đến từ một DTE, thiết bị dữ liệu đầu cuối được điều chế theo cái cách mà nó có thể được truyền dữ liệu qua các đường dây truyền dẫn. Ở một mặt khác của đường dây, một modem khác thứ hai điều chế dữ liệu đến và xúc tiến, duy trì nó.

Các modem ngày xưa chỉ tương thích cho việc gữi nhận dữ liệu. Đễ thiết lập một kết nối thì một thiết bị thứ hai như một dialer thì được cần đến. Đôi khi kết nối cũng được thiết lập bằng tay bằng cách quay số điện thoại tương ứng và một khi modem được bật thì kết nối coi như được thực thi. Các máy tính loại nhỏ ở các năm 70 thâm nhập vào thị trường là các gia đình, cùng với chi phí thì sự thiếu hụt về kiến thức kỹ thuật trở thành một vấn đề nan giải.

Một modem GSM là một modem wireless, nó làm việc cùng với một mạng wireless GSM. Một modem wireless thì cũng hoạt động giông như một modem quay số. Điểm khác nhau chính ở đây là modem quay số thì truyền và nhận dữ liệu thông qua một đường dây điện thoại cố định trong khi đó một modem wireless thì việc gữi nhận dữ liệu thông qua sóng.

Giống như một điện thoại di động GSM , một modem GSM yêu cầu 1 thẻ sim với một mạng wireless để hoạt động.

Module Sim900 là một trong những loại modem GSM. Nhưng Module Sim900 đựơc nâng cao hơn có tốc độ truyền dữ liệu nhanh hơn. Nó sử dụng hệ thống GSM/GPRS hoạt động ở băng tầng EGSM 900Mhz, DCS 1800 Mhz và PCS 1900Mhz, tính năng GPRS của Sim900 có nhiều lớp