Điện thế tại các cực của BJT:

� VE IE .R E

�V V V

� B E BE

(3.21)

V

�

� C VCC

– IC.R C

Có thể bạn quan tâm!

-

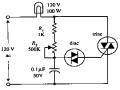

Cấu Tạo, Phân Loại Và Các Ứng Dụng Cơ Bản Của Điôt

Cấu Tạo, Phân Loại Và Các Ứng Dụng Cơ Bản Của Điôt -

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 8

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 8 -

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 9

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 9 -

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 11

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 11 -

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 12

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 12 -

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 13

Kỹ thuật điện tử cơ bản - Trường Cao đẳng Xây dựng TP. HCM Phần 1 - 13

Xem toàn bộ 114 trang tài liệu này.

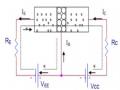

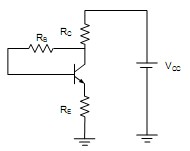

b. Dùng điện trở hồi tiếp áp RB.(hình 3-41)

Hình 3-41. Mạch phân cực BJT dạng dùng điện trở hồi tiếp áp RB.

Xét vòng mạch Bazơ- emiter ta có : V

I '.R I .R U

I .R

cc c c B B BE E E

Mặt khác : I'I I tuy nhiên I', I >> Inên I'�I

C C B C C B C C

Thay

I ' �I � I

và I

�I . Vào phương trình trên ta có :

C C B

E C

=I c.Rc UBE IC.RE IB.RB= I B..RcUBE IB.RB .IB.RE

= > I

VBB UBE

=> I

.I

BR (R R ) C B

B C E

Xét vòng mạch Collecter : VCC IC.RCVCE IE.RE

=IC.RCVCE IC.RE

=>VCE VCC IC(RC RE)

�I

VBB VBE

� B R

.(R R )

B E C

�

Tọa độ điểm phân cực Q : Q � I .I

C B

(3.22)

�V V I (R R )

�CE CC C C E

�

Phương trình đường tải tĩnh: VCE VCC IC(RCRE)

(3.23)

Nhận xét : RC,RE,VCC = const nên VCE tăng thì IC giảm và ngược lại . Vẽ đồ thị đường tải tĩnh :

IC = 0 => VCE = VCC

VCE

= 0 =>

IC

VCC RC RE

Đương tải tĩnh là đường thẳng đi qua hai điểm: A(Vcc,0) , B(

VCC RC R E

,0).

� VE = IE .R E

�

Điện thế tại các cực của BJT:

�VB VE +VBE

C CC C C�

�V V – I .R

(3.24)

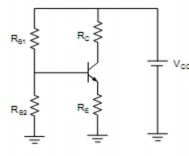

c. Dùng cầu phân thế.(hình 3-42)

Hình 3-42. Mạch phân cực dùng cầu phân thế

�V

VCC .RB 2

Áp dụng định lí Thevenin cho cầu chia áp :

��BB

�

RB 2

RB1

(3.25)

B

�R

RB1.RB2

sơ đồ tương đương :

� RB1

RB2

Hình 3.43. Mạch tương đương

Xét vòng mạch Bazơ- emiter ta có : VBB IB.RBUBE IE.RE

= IB.RBU BE (IC IB).REIB.RB UBE IB(1 ).RE

=> IB

VBB VBE

R (1 )R

=> I

C .IB

B E

Xét vòng mạch Collecter : VCC IC.RCVCE IE.RE

IC.RCVCE IC.RE

=> VCE VCC IC(RC RE) .

I

�

�

� B R

VBB VBE

(1 )R

Tọa độ điểm phân cực: Q �

B E

IC .IB

(3.26)

�V V I (R R )

�CE CC C C E

�

Phương trình đường tải tĩnh: VCE VCC IC(RCRE)

( 3.27)

Nhận xét : RC,RE,VCC = const nên VCE tăng thì IC giảm và ngược lại . Vẽ đồ thị đường tải tĩnh :

IC = 0 => VCE = VCC

VCE

= 0 =>

IC

VCC RC RE

Đương tải tĩnh là đường thẳng đi qua hai điểm: A(Vcc,0) , B(

VCC RC R E

,0).

� VE = IE .R E

�

Điện thế tại các cực của BJT:

�VB VE +VBE

C CC C C�

�V V – I .R

(3.28)

4.2.5. Các loại tranzito

Tín hiệu nhỏ Loại tranzito này thường được dùng để khuếch đại tín hiệu nhỏ nhưng cũng có thể sử dụng làm chuyển mạch. Trị số độ lợi hFE từ 10 đến 500 với dòng IC danh định cực đại vào khoảng từ 80 đến 600 mA. Tranzito này có cả hai loại npn và pnp. Tần số hoạt động cực đại là vào khoảng từ 1 đến 300 MHz.

Chuyển mạch nhỏ Các tranzito này chủ yếu dùng làm chuyển mạch

nhưng cũng có thể dùng làm khuếch đại. Trị số độ lợi hFE từ 10 đến 200 với dòng IC danh định cực đại vào khoảng từ 10 đến 100 mA. Tranzito này có cả hai loại npn và pnp, tần số hoạt động cực đại là

vào khoảng từ 1 đến 300 MHz. Tốc độ chuyển

mạch cực đại vào khoảng từ 10 đến 2000 MHz.

Tần số cao (RF) Các tranzito này được dùng cho tín hiệu nhỏ và

cũng dùng cho các ứng dụng chuyển mạch với tần số cao và tốc độ chuyển mạch lớn. Vùng cực badơ rất mỏng và kích thước của tranzito rất nhỏ. Các tranzito này có thể dùng trong các bộ khuếch đại HF, VHF, UHF, CATV và MATV và trong các máy tạo sóng. Các tranzito này có cả hai loại pnp và npn và có tần số danh định cực đại vào khoảng 2000MHz và IC cực đại từ 10 đến 600 mA.

Công suất Các tranzito này được dùng trong các bộ khuếch

đại công suất lớn và các bộ cung cấp công suất. Colectơ được kết nối với phiến kim loại để toả nhiệt. Công suất danh định vào khoảng từ 10 đến 300 W với tần số danh định vào khoảng từ 1 đến 100 MHz. Trị số dòng IC cực đại từ 1 đến 100 A. Các tranzito này có cả hai loại pnp và npn và loại Darlington (npn và pnp).

Cặp Darlington

Đây là hai tranzito trong một vỏ. Các tranzito này có độ ổn định cao, tải mức dòng lớn. Độ lợi hFE của tranzito này lớn hơn độ lợi của một tranzito. Tranzito này có cả hai loại D-npn và D-pnp.

Tranzito quang Tranzito này hoạt động như một tranzito lưỡng cực

nhạy sáng (cực badơ được lộ sáng). Khi có ánh sáng tiếp xúc với vùng cực badơ làm xuất hiện dòng badơ. Phụ thuộc vào loại tranzito quang, ánh sáng có thể tác động như là tác nhân định thiên (tranzito hai chân).

Dãy tranzito

Loại bao gói này có nhiều tranzito kết hợp trong một vỏ bọc tích hợp. Ví dụ, một dãy tranzito ở đây được chế tạo gồm 3 tranzito npn và 2 tranzito pnp.

5. Tranzitor hiệu ứng trường

Mục tiêu:

- Trình bầy được cấu tạo , nguyên lý hoạt động của JFET, MOSFET

- Vẽ được sơ đồ cách mắc và nêu được đặc tuyến của JFET, MOSFET

Transistor trình bày trước được gọi là transistor mối nối lưỡng cực (BJT = Bipolar Junction Transistor). BJT có điện trở ngõ vào nhỏ ở cách mắc thông thường CE, dòng IC = IB, muốn cho IC càng lớn ta phải tăng IB (thúc dòng lối vào). Đối với transistor hiệu ứng trường có tổng trở vào rất lớn. Dòng điện ở lối ra được tăng bằng cách tăng điện áp ở lối vào mà không đòi hỏi dòng điện. Vậy ở loại này điện áp sẽ tạo ra một trường và trường này tạo ra một dòng điện ở lối ra.

Field Effect Transistor (FET)

FET có hai loại: JFET v à MOSFET.

5.1.JFET

5.1.1.Cấu tạo – kí hiệu

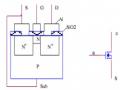

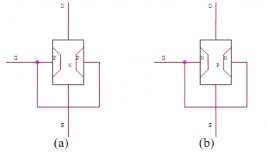

JFET (Junction Field Effect Transistor) được gọi là FET nối. JFET có cấu tạo như (hình 3-44)

Hình3-44. Cấu tạo của JFET kênh N (a), JFET kênh P (b).

Trên thanh bán dẫn hình trụ có điện trở suất khá lớn (nồng độ tạp chất tương đối thấp), đáy trên và đáy dưới lần lượt cho tiếp xúc kim loại đưa ra hai cực tương ứng là cực máng (cực thoát) và cực nguồn.

Vòng theo chu vi của thanh bán dẫn người ta tạo một mối nối P – N. Kim loại tiếp xúc với mẫu bán dẫn mới, đưa ra ngoài cực cổng (cửa).

D: Drain: cực máng (cực thoát). G: Gate: cực cổng (cực cửa).

S: Source: cực nguồn.

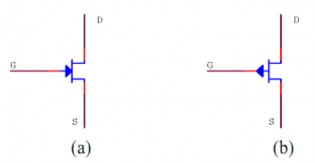

Vùng bán dẫn giữa D và S được gọi là thông lộ (kênh). Tùy theo loại bán dẫn giữa D và S mà ta phân biệt JFET thành hai loại: JFET kênh N, JFET kênh P. Nó có kí hiệu như (hình 3-45)

Hình 3-45 . Kí hiệu của JFET kênh N (a), JFET kênh P (b).

5.1.2. Nguyên lí hoạt động

Giữa D và S đặt một điện áp VDS tạo ra một điện trường có tác dụng đẩy hạt tải đa số của bán dẫn kênh chạy từ S sang D hình thành dòng điện ID. Dòng ID tăng theo điện áp VDS đến khi đạt giá trị bão hòa IDSS (saturation) và điện áp tương ứng gọi là điện áp thắt kênh VPO (pinch off), tăng VDS lớn hơn VPO thì ID vẫn không tăng. Giữa G và S đặt một điện áp VGS sao cho không phân cực hoặc phân cực nghịch mối nối P – N. Nếu không phân cực mối nối P – N ta có dòng ID đạt giá trị lớn nhất IDSS. Nếu phân cực nghịch mối nối P – N làm cho vùng tiếp xúc thay đổi diện tích. Điện áp phân cực nghịch càng lớn thì vùng tiếp xúc (vùng hiếm) càng nở rộng ra, làm cho tiết diện của kênh dẫn bị thu hẹp lại, điện trở kênh tăng lên nên dòng điện qua kênh ID giảm xuống và ngược lại. VGS tăng đến giá trị VPO thì ID giảm

về 0.

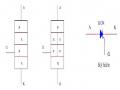

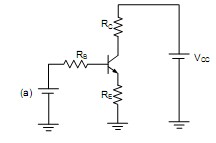

5.1.3.Cách mắc JFET

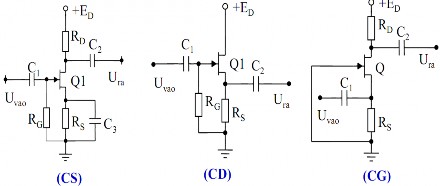

- Cũng tương tự như BJT, JFET cũng có 3 cách mắc chủ yếu là: Chung cực nguồn(CS), chung cực máng (DC), và chung cực cửa(CG)

- Trong đó kiểu CS thường được dùng nhiều hơn cả vì kiểu mắc này cho hệ số khuếch đại điện áp cao, trở kháng vào cao. Còn các kiểu mắc CD, CG thường được dùng trong tầng khuếch đại đệm và khuếch đại tần số cao. (hình 3-46)

Hình 3-46. Các cách mắc của JFET

- CS: Tín hiệu vào G so với S, tín hiệu ra D so với S.

- CG: Tín hiệu vào S so với G, tín hiệu ra D so với G.

- CD: Tín hiệu vào G so với D, tín hiệu ra S so với D.

5.1.3. Đặc tuyến của JFET.(hình 3-47)

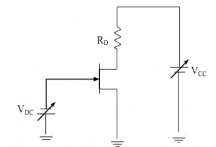

Hình 3-47. Mạch khảo sát đặc tuyến của JFET.

Khảo sát sự thay đổi dòng thoát ID theo hiệu điện thế VDS và VGS, từ đó người ta đưa ra hai dạng đặc tuyến của JFET.

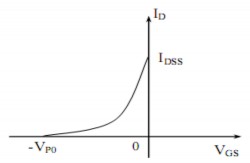

a. Đặc tuyến truyền dẫn ID(VGS) ứng với VDS = const.

Giữ VDS = const, thay đổi VGS bằng cách thay đổi nguồn VDC, khảo sát sự biến thiên của dòng thoát ID theo VGS. Ta có:

ID I

DSS

(1 VGS )2

VP 0

- Khi VGS = 0V, dòng điện ID lớn nhất và đạt giá trị bão hòa, kí hiệu: IDSS.

- Khi VGS âm thì dòng ID giảm, VGS càng âm thì dòng ID càng giảm. Khi VGS = VPO thì dòng ID = 0. VPO lúc này được gọi là điện thế thắt kênh (nghẽn kênh).

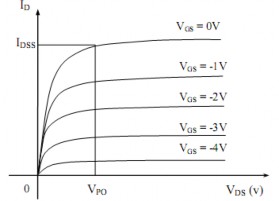

b. Đặc tuyến ngõ ra ID(VDS) ứng với VGS = const.

Giữ nguyên VGS ở một trị số không đổi (nhất định). Thay đổi VCC và khảo sát sự biến thiên của dòng thoát ID theo VDS. .(hình 3-48)

Hình 3-48. Đặc tuyến truyền dẫn của JFET.

- Giả sử chỉnh nguồn VDC về 0v, không thay đổi nguồn VDC, ta có VGS =

0V = const. Thay đổi nguồn VCC → VDS thay đổi → ID thay đổi. Đo dòng ID và VDS. Ta thấy lúc đầu ID tăng nhanh theo VDS, sau đó ID đạt giá trị bão hòa, ID không tăng mặc dù VDS cứ tăng.

- Chỉnh nguồn VDC để có VGS = 1v. Không thay đổi nguồn VDC, ta có VGS =

1V = const. Thay đổi nguồn VCC → VDS thay đổi → ID thay đổi. Đo dòng ID và VDS tương ứng. Ta thấy lúc đầu ID tăng nhanh theo VDS, sau đó ID đạt giá trị bão hòa, ID không tăng mặc dù VDS cứ tăng.

- Lặp lại tương tự như trên ta vẽ được họ đặc tuyến ngõ ra ID(VDS) ứng với VGS = const. .(hình 3-49)

Hình 3-49. Họ đặc tuyến ngõ ra của JFET.

5.2. MOSFET (Metal Oxide Semiconductor FET)

MOSFET hay còn được gọi IGFET (Insulated Gate FET) là FET có cực cổng cách li. MOSFET chia làm hai loại: MOSFET kênh liên tục (MOSFET loại hiếm)