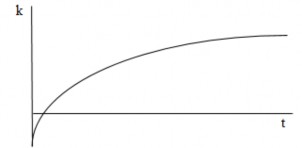

đây nhất sử dụng và có thể các lần truy cập khác nữa, cho nên w (k,t) là một hàm đơn điệu tăng của k. Tuy nhiên giới hạn của w (k,t) khi k cứ tăng dần lên hữu hạn,bởi vì một chương trình không thể tham khảo nhiều trang hơn số trang của không gian địa chỉ của nó. Có số ít chương trình chỉ sử dụng một trang.

Hình 4.61 miêu tả kích thước của tập làm việc là của k. Trong thực tế hầu hết các chương trình truy cập ngẫu nhiên có số ít các trang nhưng tập này thay đổi chậm theo thời gian, điều đó giải thích cho sự tăng nhanh ban đầu của đường cong và sau đó

Ví dụ một chương trình đang thi hành một vòng lặp chiếm hai trang, chương trình sử dụng dữ liệu chiếm bốn trang, nó có thể tham khảo cả sáu trang cứ mỗi khi thi hành 1000 chỉ thị. Tuy nhiên lần tham khảo mới nhất tới một trang khác nào đó có thể là tham khảo một triệu tới trang đó tính từ lúc chương trình bắt đầu chạy. Do hành trạng có tính tiệm cận này nên nội dung của của tập làm việc không nhạy cảm đối với giá trị đã được chọn của k, hay nói một cách khác, tồn tại một miền rộng các giá trị của k trong đó working set là không thay đổi.

Hình 4. 61. Hàm w (k, t) là kích thước của tập làm việc tại thời điểm t

Lợi ích của phương pháp mô hình tập làm việc

Vì tập làm việc thay đổi chậm theo thời gian, cho nên có thể đoán ra các trang nào sẽ cần đến khi một chương trình được cho chạy trở lại dựa trên tập làm việc của lần chạy trước đó. Các trang này có thể được nạp vào trong khi một chương trình khác nào đó vẫn còn đang chạy, trước khi chương trình được cho chạy trở lại, nó sẽ không sinh ra ngay lập tức một số lớn các lỗi trang làm lãng phí thời gian.

Người ta đã biết rằng thời gian cần để đọc một trang từ đĩa vào bộ nhớ chính thường bằng hoặc lớn hơn thời gian thực hiện 20.000 chỉ thị.

Nhược điểm của phương pháp sử dụng tập làm việc

Nếu tập làm việc được đưa vào bộ nhớ chính trước khi một chương trình được cho chạy trở lại, nhưng chương trình này khi chạy lại cần một tập làm việc khác (chương trình nằm ở lúc chuyển đổi giữa tập làm việc này và tập làm việc khác), thì việc nạp trước đó là thừa, và chương trình vẫn phải đợi cho đến khi các trang mà nố cần được nạp vào.

Có thể bạn quan tâm!

-

Kiến trúc máy tính - 21

Kiến trúc máy tính - 21 -

Kiến trúc máy tính - 22

Kiến trúc máy tính - 22 -

Phương Pháp Cấp Trang Khi Có Yêu Cầu Và Mô Hình Tập Làm Việc

Phương Pháp Cấp Trang Khi Có Yêu Cầu Và Mô Hình Tập Làm Việc -

Giao Diện Giữa Bộ Xử Lý Với Các Bộ Phận Vào/ Ra

Giao Diện Giữa Bộ Xử Lý Với Các Bộ Phận Vào/ Ra -

Kiến trúc máy tính - 26

Kiến trúc máy tính - 26 -

Kiến trúc máy tính - 27

Kiến trúc máy tính - 27

Xem toàn bộ 233 trang tài liệu này.

Theo phương pháp cấp trang khi có yêu cầu thì tình huống này không thể xảy ra, các ttrang được nạp vào là các trang thực sự cần đến. Hiện nay người ta vẫn còn tranh luận về phẩm chất của hai chiến lược này.

CÂU HỎI ÔN TẬP CHƯƠNG 4

Câu 1:

Nêu các đặc trưng của hệ thống nhớ. Trình bày sự phân cấp bộ nhớ trong máy tính.

Câu 2:

Trình bày các điểm giống và khác nhau của SRAM và DRAM. Tại sao DRAM có tốc độ truy cập chậm hơn SRAM? Trong máy tính, SRAM và DRAM được ứng dụng cho các loại bộ nhớ nào?

Câu 3.

Trình bày kỹ thuật ánh xạ địa chỉ trực tiếp từ bộ nhớ chính vào bộ nhớ cache.

Câu 4:

Trình bày kỹ thuật ánh xạ địa chỉ liên kết tập hợp từ bộ nhớ chính vào bộ nhớ cache.

Câu 5:

Trình bày kỹ thuật ánh xạ địa chỉ liên kết hoàn toàn từ bộ nhớ chính vào bộ nhớ cache. Hãy cho biết ưu và nhược điểm của kỹ thuật ánh xạ này.

Câu 6:

Nêu khái niệm trúng cache, trượt cache; nguyên lý định vị tham số bộ nhớ. Trình bày nguyên tắc thiết kế, trao đổi thông tin giữa cache và bộ nhớ chính.

Câu 7:

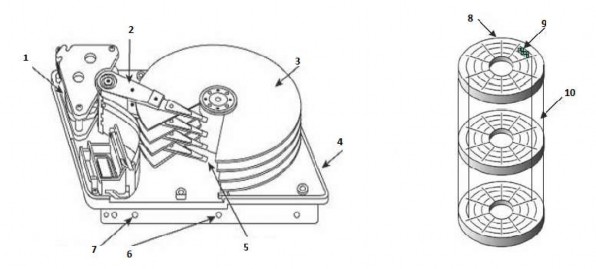

Nêu chức năng và định dạng vật lý trên đĩa cứng. Hãy điền tên ứng với các bộ phận của ổ đĩa cứng được đánh số thứ tự ở hình dưới đây.

Câu 8:

Cho một IC ROM có các chân địa chỉ là A0 đến A13 và các chân dữ liệu là D0 đến D7.

a) Trình bày cách tổ chức bộ nhớ của IC ROM.

b) Tính dung lượng của IC ROM.

Câu 9:

Cho vi mạch nhớ DRAM 16Mb có 4 chân dữ liệu. Hãy xác định:

a) Số chân địa chỉ.

b) Cách tổ chức bộ nhớ.

Câu 10:

Cho vi mạch nhớ SRAM 1Mb có 8 chân dữ liệu

a) Trình bày cách tổ chức bộ nhớ của SRAM.

b) Xác định số chân địa chỉ.

Câu 11:

Cho vi mạch nhớ DRAM 128Mb có 8 chân dữ liệu. Hãy xác định:

a) Số chân địa chỉ.

b) Cách tổ chức bộ nhớ.

Câu 12:

Cho vi mạch nhớ SRAM 512Kb có 4 chân dữ liệu

a) Trình bày cách tổ chức bộ nhớ của SRAM

b) Xác định số chân địa chỉ

Câu 13:

Cho bộ nhớ chính có dung lượng 512MB, bộ nhớ cache có dung lượng 256KB, kích thước line trong bộ nhớ cache là 64B, độ dài ngăn nhớ 2B. Hãy xác định các trường địa chỉ do bộ vi xử lý phát ra.

Câu 14:

Cho bộ nhớ chính có dung lượng 256MB, bộ nhớ cache có dung lượng 128KB, kích thước line trong bộ nhớ cache là 16B, độ dài ngăn nhớ 8B. Hãy xác định các trường địa chỉ do bộ vi xử lý phát ra.

Câu 15:

Máy tính có bộ nhớ chính dung lượng 4GB, bộ nhớ cache dung lượng 512KB, kích thước line trong bộ nhớ cache là 64B, độ dài ngăn nhớ là 16B. Bộ nhớ cache sử dụng phương pháp ánh xạ trực tiếp. Hãy tìm dạng địa chỉ do bộ vi xử lý phát ra.

Câu 16:

Bộ nhớ chính của máy tính có dung lượng là 512MB, bộ nhớ cache có dung lượng là 128 KB, kích thước line là 32B và mỗi set có 8 line, độ dài ngăn nhớ là 1B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong trường hợp ánh xạ liên kết tập hợp.

Câu 17:

Bộ nhớ chính của máy tính có dung lượng là 256MB, bộ nhớ cache có dunglượng là 128 KB, kích thước line là 64B và mỗi set có 4 line, độ dài ngăn nhớ là

4B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong trường hợp ánh xạ liên kết tập hợp.

Câu 18:

Bộ nhớ chính của máy tính có dung lượng là 2GB, bộ nhớ cache có dung lượng là 2MB, kích thước line là 128B và mỗi set có16line, độ dài ngăn nhớ là 8B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong trường hợp ánh xạ liên kết tập hợp.

Câu 19:

Máy tính có bộ nhớ chính dung lượng là 256MB, dung lượng bộ nhớ cache là 128 KB, kích thước line là 32B, độ dài ngăn nhớ là 4B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong kỹ thuật ánh xạ liên kết hoàn toàn.

Câu 20:

Máy tính có bộ nhớ chính dung lượng là 512MB, dung lượng bộ nhớ cache là 128KB, kích thước line là 32B, độ dài ngăn nhớ là 8B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong kỹ thuật ánh xạ liên kết hoàn toàn.

Câu 21:

Máy tính có bộ nhớ chính dung lượng là 1GB, dung lượng bộ nhớ cache là 256 KB, kích thước line là 64B, độ dài ngăn nhớ là 4B. Hãy xác định số bit cho mỗi trường của địa chỉ do CPU phát ra trong kỹ thuật ánh xạ liên kết hoàn toàn.

Câu 22:

a)Xác định số chân địa chỉ và dữ liệu ở vi mạch nhớ DRAM 16Kx4, SRAM 16Kx4.

b)So sánh cách tổ chức bộ nhớ của SRAM và DRAM.

Câu 23:

Cho chip nhớ SRAM có dung lượng 8K x 4 bit. Hãy thiết kế mô-đun nhớ có dung lượng 8K x 8 bit.

Câu 24:

Cho chip nhớ SRAM có dung lượng 4K x 4 bit. Hãy thiết kế mô-đun nhớ có dung lượng 32K x 8 bit.

Câu 25:

Cho chip nhớ SRAM có dung lượng 8K x 4 bit. Hãy thiết kế mô-đun nhớ có dung lượng 16K x 16 bit.

Câu 26:

Cho chip nhớ SRAM có dung lượng 1M x 2 bit. Hãy thiết kế mô-đun nhớ có dung lượng 4M x 2 bit.

Câu 27:

Cho chip nhớ SRAM có dung lượng 4M x 2 bit. Hãy thiết kế mô-đun nhớ có dung lượng 4M x 10 bit.

Câu 28:

Bộ nhớ ảo của máy tính là gì? Tại sao cần sử dụng bộ nhớ ảo?

Câu 29:

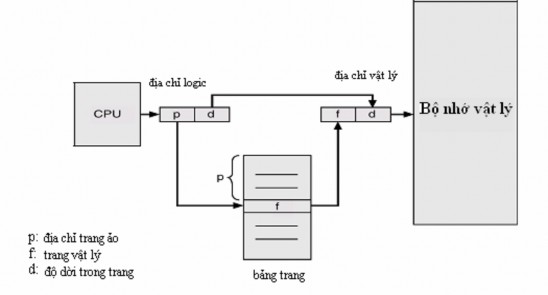

Cho sơ đồ chuyển đổi địa chỉ trong hình

a) Giải thích sơ đồ hình

b) Biết p=12, d=345, kích thước trang là 1KB, trang 12 nằm ở khung trang 5, trang đầu tiên bắt đầu từ địa chỉ 0, hãy tính địa chỉ vật lý.

Câu 30:

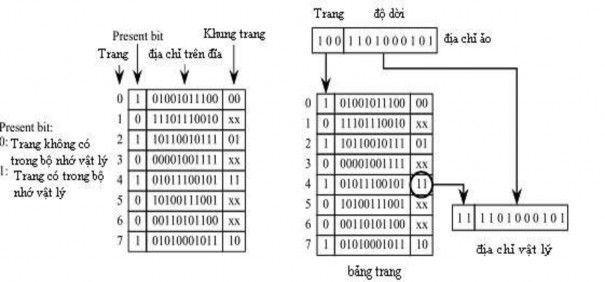

Cho sơ đồ ánh xạ địa chỉ giữa bộ nhớ ảo và bộ nhớ vật lý trong định vị trang như hình sau:

Vẽ sơ đồ chuyển đổi địa chỉ và xác định địa chỉ trang ảo và trang vật lý trong sơ đồ.

Câu 31:

Bộ nhớ ảo có kích thước 64KB được chia thành các trang có kích thước 4KB. Hãy xác định giá trị các bit trong các trường của địa chỉ ảo 16 bit có giá trị thập phân là 12310.

Câu 32:

Một hệ thống máy tính sử dụng bộ nhớ ảo với cơ chế phân trang có cấu hình như sau: địa chỉ logic 32 bit, kích thước bộ nhớ RAM là 512MB, kích thước trang là 4096 byte, kích thước bộ nhớ ảo là 1GB. Hãy xác định:

a) Số khung trang của hệ thống.

b) Số trang trong không gian địa chỉ của bộ nhớ ảo.

CHƯƠNG 5 : HỆ THỐNG BUS VÀ TỔ CHỨC VÀO/ RA

5.1. Nguyên tắc giao tiếp với thiết bị ngoại vi

Máy tính muốn trao đổi thông tin với thế giới bên ngoài thì phải thông qua hệ thống vào/ ra. Thành phần chính của hệ thống vào/ ra trong máy tính bao gồm các thiết bị ngoại vi (Peripheral Devices) và các mô-đun vào/ ra (I/ O Mô-đun)

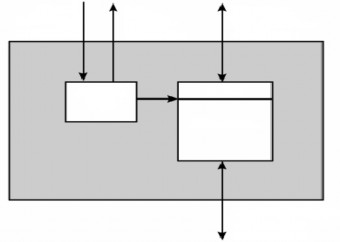

- Cấu trúc cơ bản của hệ thống vào/ ra:

Hình 5. 1. Cấu trúc hệ thống vào/ ra

- Thiết bị ngoại vi (TBNV) có chức năng chuyển đổi dữ liệu giữa bên trong và bên ngoài máy tính. Người ta phân loại thiết bị ngoại vi như sau:

+ Thiết bị vào: bàn phím, chuột, máy quét …

+ Thiết bị ra: màn hình, máy in …

+ Thiết bị nhớ: các ổ đĩa …

Các thành phần cơ bản của thiết bị ngoại vi:

Bộ chuyển đổi tín hiệu (transducer): chuyển đổi dữ liệu từ dạng tín hiệu điện thành dạng năng lượng khác và ngược lại

Logic điều khiển (control logic): điều khiển hoạt động của TBNV đáp ứng theo yêu cầu từ mô-đun vào/ra.

Bộ đệm (buffer): chứa dữ liệu tạm thời khi trao đổi dữ liệu giữa mô-đun vào/ra và TBNV.

TÝn hiÖu §K tò Modul vµo/ra

TÝn hiÖu TT

®Òn Modul vµo/ra

D÷ liÖu ®Òn vµ tò Modul vµo/ra

Logic §K

Bé ®Öm

Bé chuyÓn

®æi tÝn hiÖu

D÷ liÖu ®Òn vµ tò m«i tr•êng bªn ngoµi

Hình 5. 2. Các thành phần thiết bị ngoại vi

- Nguyên tắc giao tiếp với thiết bị ngoại vi

Bộ xử lý dùng 2 cách để liên lạc với các bộ phận vào/ ra:

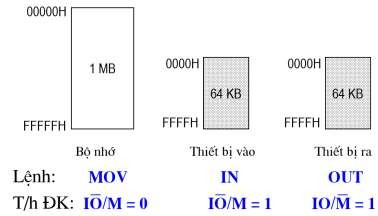

Cách thứ nhất, thường được dùng: là cách dùng một vùng địa chỉ của bộ nhớ làm vùng địa chỉ của các ngoại vi. Khi đọc hay viết vào vùng địa chỉ này của bộ nhớ là liên hệ đến các ngoại vi. Cách này còn gọi là phương pháp địa chỉ hóa cổng vào/ ra cách biệt.

+ Đặc điểm: Không gian địa chỉ cổng vào/ra nằm ngoài không gian địa chỉ bộ nhớ.

+ Cách truy nhập:Cần có tín hiệu phân biệt truy nhập cổng vào/ra hay truy nhập bộ nhớ. Sử dụng lệnh vào/ra chuyên dụng: IN, OUT.

Hình 5. 3. Vào/ ra cách biệt đối với CPU 8088

Cách thứ hai, dùng mã lệnh riêng biệt cho vào/ ra (tức là có các lệnh vào/ ra riêng, không trùng với lệnh đọc hay viết vào ô nhớ). Trong trường hợp này, bộ xử lý gởi một tín hiệu điều khiển cho biết địa chỉ đang dùng là của một ngoại vi.. Cách này còn gọi là phương pháp địa chỉ hóa cổng vào/ ra bằng bảng nhớ.

+ Đặc điểm: Không gian địa chỉ cổng vào/ra nằm trong không gian địa chỉ bộ nhớ.

+ Cách truy nhập: