Hình 4.3 Sơ đồ khối chuyển mạch không gian

Chuyển mạch không gian tín hiệu TDMsố thường thiết lập đồng thời một số

lượng lớn các cuộc nối qua ma trận với tốc độ tức thì trong một khung tín hiệu 125 s,

trong đó mỗi cuộc nối qua ma trận tồn tại trong thời gian của một khe thời gian TS. Một cuộc gọi điện thoại có thể kéo dài trong khoảng thời gian nhiều khung tín hiệu

PCM (thông thường khoảng 1,4÷2,4 triệu khung và tương

ứng với khoảng từ

3÷5

phút). Do vậy một kiểu điều khiển theo chu kỳ đơn giản cho một mẫu nối là cần thiết. Điều này dễ dàng đạt được nhờ một bộ nhớ RAM điều khiển cục bộ liên quan tới ma trận chuyển mạch không gian.

Chuyển mạch không gian có kích thước trường chuyển mạch là MxN. Trong đó có các đường điều khiển để điều khiển các nút chuyển mạch đóng tiếp điểm tương ứng tại thời điểm phù hợp. Nếu chuyển mạch S là điều khiển đầu vào (lựa chọn 1 trong số M đầu vào để đưa ra 1 đầu ra), nếu là điều khiển đầu ra (lựa chọn 1 đầu vào để đưa ra 1 trong N đầu ra). Trên thực tế thường chọn M=N. Ngoài ra còn có tín hiệu cho phép ghi vào bộ nhớ W tại thời điểm thực hiện đóng nút chuyển mạch, và tín hiệu địa chỉ của nút điều khiển và xung đồng hồ đồng bộ.

4.2.1.2 Cấu tạo (điều khiển đầu vào)

4.2.1.2.1 Sơ đồ nguyên lý chuyển mạch S

PCM O

PCM O

PCM O

PCM O

PCM n×TS

n1 i 1 0 TS

PCM I1

PCM I

i 1 2 3 N

A

A

A

A0 0 0 0

A2

A2=1

2

A

1

PCM I

A1

A1

A1

CM1.i=0011

Với n=32

3

A2 A2 A2 A2

M

PCM I

A

M1

AM1

AM1

AM1

LOC1

Counter

Add R/W

0 0 1 1

Selector

DEC

L

0 O

i C

n1 2

L L

O … O

C C

3 N

Clk

CM1

W Data

Hình 4.4 Nguyên lý chuyển mạch không gian S

Trường chuyển mạch không gian số S thực hiện quá trình chuyển nội dung thông tin từ các tuyến PCM đầu vào tới các tuyến PCM đầu ra mà không làm thay đổi vị trí khe thời gian trên trục thời gian. Để tạo ra kênh truyền thông cho các cuộc gọi, các thông tin được chuyển qua trường chuyển mạch S với chu kỳ 125μs.

Hình 4.3 minh họa nguyên tắc cấu tạo và hoạt động của một tầng chuyển mạch không gian S. Chuyển mạch tầng S cấu tạo từ 2 thành phần cơ bản: Ma trận chuyển mạch và khối điều khiển chuyển mạch cục bộ LOC.

4.2.1.2.2 Chức năng các thành phần chính

* Khối ma trận chuyển mạch ( Switching Matrix):

Khối ma trận chuyển mạch được cấu trúc dưới dạng ma trận hai chiều gồm các cổng đầu vào và các cổng đầu ra, trên các cổng là các tuyến PCM có chu kỳ khung 125μs. Các điểm nối trong ma trận là các phần tử logic không nhớ ( thông thường là các mạch AND). Một ma trận có (M) cổng đầu vào và (N) cổng đầu ra trở thành ma trận vuông khi M=N.

Số lượng phần tử AND điều khiển bởi LOC = số luồng PCM đầu vào = M

* Khối điều khiển khu vực LOC:

Khối điều khiển khu vực gồm một số khối thiết bị như:

Bộ nhớ điều khiển kết nối CM (Control Memory) lưu trữ các thông tin điều khiển theo chương trình ghi sẵn cho ma trận chuyển mạch, nội dung thông tin trong CM sẽ thể hiện vị trí tương ứng của điểm kết nối của cột cần chuyển mạch.

+ Số ngăn nhớ của CM = số lượng khe thời gian của luồng PCM = n,

+ Dung lượng một ngăn nhớ = Số lượng ô nhớ trong ngăn nhớ = L = [ log2M] (bit) phần nguyên lớn hơn gần nhất);

Bộ giải mã địa chỉ DEC (DECoder) là mạch ghép của các bộ giải mã địa chỉ x toy, (cặp x, y phụ thuộc vào kích thước ma trận chuyển mạch, có các loại 2to4, 3 to8, 4to16). DEC chuyển các tín hiệu điều khiển dạng mã nhị phân (x bit) thành các tín hiệu "1" cho phép cổng AND ứng với thông tin địa chỉ trong CM; Nếu kích thước ma trận chuyển mạch yêu cầu lớn hơn 16 có thể được ghép nhiều module 4to16 lại.

Bộ đếm khe thời gian (Counter) nhận tín hiệu đồng hồ từ đồng hồ hệ thống cấp các xung đồng bộ cho bộ điều khiển theo đồng bộ của các tuyến PCM vào và ra. Bộ đếm có chu kỳ đếm theo số lượng khe thời gian trong luồng PCM. Số bit địa chỉ của bộ đếm = Log2n.

Bộ đếm đưa tín hiệu đồng bộ vào bộ lựa chọn (Selector) để đồng bộ quá trình ghi dịch địa chỉ và tác vụ ghi đọc của bộ nhớ CM.

4.2.1.3 Nguyên lý hoạt động của chuyển mạch S

Nguyên lý hoạt động của trường chuyển mạch không gian S gồm một số bước cơ bản sau:

Các tuyến PCM trên các cổng đầu vào và đầu ra được đồng bộ hoá theo tín hiệu đồng bộ. Như trên hình 4.3 chỉ ra mỗi khối điều khiển khu vực LOC đảm nhiệm một cổng đầu ra, vì vậy số bộ điều khiển LOC sẽ bằng đúng số cổng đầu ra (N bộ điều khiển).

Để rõ hơn nguyên tắc điều khiển và hoạt động của trường chuyển mạch S, ta xét một ví dụ cụ thể: Yêu cầu chuyển nội dung thông tin trên TSi tại cổng số 3 đầu vào (I3) tới TSi trên cổng số 1 đầu ra (O1). (TSi I3 > TSi O1)

Quá trình ghi thông tin vào CM: Với yêu cầu trên, khối điều khiển khu vực (ứng

với đầu ra O1) LOC1 sẽ được chọn để thực hiện nhiệm vụ điều khiển chuyển mạch,

thông tin điều khiển được ghi vào CM thông qua đường dữ liệu điều khiển Data,

thanh ghi địa chỉ

của bộ chọn Selector trỏ

đến ngăn nhớ

i: tương

ứng với TSi của

khung PCM, nội dung dữ liệu điều khiển thể hiện địa chỉ A2 của cổng AND ứng với đầu vào 3.

Quá trình đọc thông tin từ CM: Qua sự phối hợp đồng bộ của bộ đếm, một chu trình điều khiển tuần tự và đồng bộ giữa chỉ số khe thời gian và con trỏ địa chỉ để đọc dữ liệu ra từ CM. Vì vậy, khi con trỏ chỉ đến địa chỉ ngăn nhớ i, thời gian hệ thống sẽ trùng khớp với TSi trên các tuyến PCM, đồng thời Selector chỉ thị quá trình đọc dữ liệu và chuyển thông tin dữ liệu (trong ngăn nhớ i) qua bộ DEC để giải mã địa chỉ, DEC thực hiện đóng tiếp điểm của cổng AND có địa chỉ A2="1" giữa cổng vào 3 và cổng ra

1. Tiếp điểm được đóng trong suốt thời gian chuyển dữ liệu và bằng thời gian của khe thời gian (8 bit = 3,9 μs). Với tính chất logic của tiếp điểm AND, khi hàm điều khiển có mức "1" thì toàn bộ số liệu đầu vào sẽ được chuyển tới đầu ra.

Đối với mỗi một cuộc nối thoại, chu kỳ đóng tiếp điểm được thực hiện tuần tự theo chu kỳ 125μs, việc ngắt các kết nối được thực hiện đơn giản thông qua quá trình ghi lại dữ liệu trong bộ nhớ CM, các khoảng thời gian còn lại sẽ được thực hiện cho các kết nối khác. Nếu ma trận chuyển mạch là ma trận vuông thì tổng số kênh tối đa có thể kết nối đồng thời sẽ là Ch= n x M (n: số khe thời gian trong một khung PCM; M: số cổng đầu vào chuyển mạch S).

Trường chuyển mạch không gian S mang tính thời gian thực nếu xét về tính chu kỳ của quá trình đóng ngắt tiếp điểm, tuy nhiên chu kỳ này là cố định cho tất cả các cuộc nối qua trường chuyển mạch. Nhược điểm luôn tồn tại trong các trường chuyển mạch không gian S là khả năng tắc nghẽn khi có nhiều hơn một yêu cầu chuyển mạch TS đầu vào cùng muốn ra một cổng đầu ra. Một ma trận chuyển mạch không tắc nghẽn hoàn toàn được định nghĩa là một ma trận có khả năng đáp ứng được các kết nối từ các đầu vào bất kỳ tới các đầu ra bất kỳ.

Hiện tượng tranh chấp cổng đầu ra trong nội bộ trường chuyển mạch được gọi là hiện tượng tắc nghẽn nội. Để giải quyết vấn đề trên, các trường chuyển mạch S thường được kết hợp với các bộ đệm gây trễ thời gian để tránh tranh chấp, giải pháp ghép nối với trường chuyển mạch thời gian T được sử dụng phổ biến trong các hệ thống chuyển mạch hiện nay.

4.2.1.4 Chuyển mạch song song

* Chuyển mạch song song

Khi phải chuyển mạch với luồng PCM có số lượng khe thời gian lớn (PCM

1024) thì thời gian để thực hiện chuyển mạch cho 1 khe thời gian (1TS) sẽ rất nhỏ

(với PCM 1024: 1TS chiếm 0,122 s, 1 bit chiếm 15,25ns).

Với khe thời gian rất ngắn thì các bít thông tin dễ bị biến dạng do tốc độ chuyển mạch quá nhỏ (tốc độ hoạt động của các cổng logic trong chuyển mạch) => dễ làm bị thất thoát thông tin.

Để khắc phục nhược điểm này: người ta thực hiện chuyển thông tin từ nối tiếp của một khe thời gian thành song song ở đầu vào của chuyển mạch S và ngược lại. Khi đó thời gian tồn tại 1 bít (độ rộng xung) tăng lên 8 lần => làm giảm sự thất thoát thông tin => tăng được tốc độ chuyển mạch.

Bộ chuyển đổi nối tiếp/song song (S/P), song song/nối tiếp (P/S) có thể sử dụng bộ ghi dịch và hoạt động theo xung nhịp của tổng đài.

Bộ chuyển mạch gồm có 8 tầng song song, mỗi tầng chuyển mạch cho 1 bít

thuộc 1TS => làm tăng tốc độ chuyển mạch (do 1 bít có độ rộng xung lớn) khi qua các cổng logic không bị biến dạng và không bị ảnh hưởng do trễ tín hiệu.

b

bit# ![]()

bit*

Chuyển đổi nối tiếp nong song S/P

Chuyển đổi song song nối tiếp P/S

#0

Chuyển mạch không gian (8×8)

b #0

b b

#7 #7

Hình 4.5 Cấu trúc tổng quát của chuyển mạch song song

Phía đầu vào và đầu ra thực hiện ngược nhau để đảm bảo tín hiệu trên đường truyền là tín hiệu nối tiếp.

Khi thực hiện chuyển đổi như trên kích thước chuyển mạch giảm đi đáng kể. Ví dụ, thay vì thiết kế trường chuyển mạch có kích thước 32×32 luồng PCM 32 vào và ra, số tiếp điểm là 1024, chỉ cần ghép 32 luồng thành các nhóm 8. Kích thước trường chuyển mạch S chỉ còn là 4×4 luồng PCM 32×8.

* Chuyển mạch song song ghép từ các khối

Vì kích thước của ma trận chuyển mạch S chỉ có giới hạn, ví dụ, 16×16 tức là chỉ điều khiển tối đa được ma trận S có kích thước 16×16. Để giải quyết vấn đề mở rộng ma trận chuyển mạch không gian S thì cần phải ghép các khối nhỏ lại với nhau.

MUDXEMUX

MUDXEMUX

MUX

DEMUX

Chuyển mạch S dùng MUX, DEMUX

PCM I

PCM O'

PCM O1

PCM O2 PCM ON PCM I'

PCM I'1 PCM I'2 N

Hình 4.6 Chuyển mạch S dùng Mux, Demux

Chuyển mạch S dùng các module

1

n

PCM I 1

n×k n

1

n

1

SS

11

SS

21

SS

1n

n×n

n×n

n×n

SS

21

SS

22

SS

2n

n×n

8×8

n×n

SS

k1

SS

k2

SS

kn

n×n

n×n

n×n

n

1 PCM O k×n

n 1

n

Hình 4.7 Chuyển mạch S dùng các module

4.2.1.2 Trường chuyển mạch thời gian

4.2.2.1 Khái quát về chuyển mạch thời gian T

Chúng ta nhận thấy rằng cấu tạo và hoạt động của chuyển mạch tầng S chỉ thực hiện cho các quá trình chuyển mạch có cùng chỉ số khe thời gian giữa đường PCM vào và đường PCM ra. Trong trường hợp tổng quát có yêu cầu trao đổi khe thời gian giữa đầu vào và đầu ra khác nhau thì phải ứng dụng tầng chuyển mạch thời gian T (Time Switching Stage).

PCM O

TS

j

Bộ nhớ thoại SM

Điều khiển chuyển mạch T

Trường chuyển mạch thời gian tín hiệu số thực hiện quá trình chuyển đổi nội dung thông tin từ một khe thời gian này sang khe thời gian khác của một luồng PCM, dựa trên nguyên tắc gây trễ cho các tín hiệu. Để gây trễ thì phải có bộ nhớ để lưu trữ các thông tin thoại trong các khe thời gian gọi là bộ nhớ thoại SM (Speech Memory). Quá trình gây trễ tín hiệu được thực hiện theo nguyên tắc trao đổi khe thời gian nội TSI. Để điều khiển các quá trình trao đổi các khe thời gian có các bộ nhớ điều khiển.

TS i |

Có thể bạn quan tâm!

-

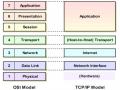

Cấu Trúc Các Lớp Và Các Bản Tin

Cấu Trúc Các Lớp Và Các Bản Tin -

Phương Thức Đồng Bộ Chủ Tớ (Master Slaver Synchronization)

Phương Thức Đồng Bộ Chủ Tớ (Master Slaver Synchronization) -

Điều Khiển Kết Cuối Đơn Trong Đồng Bộ Tương Hỗ

Điều Khiển Kết Cuối Đơn Trong Đồng Bộ Tương Hỗ -

Giá Trị Các Ngăn Nhớ Và Tiến Trình Xử Lý Tại Tst

Giá Trị Các Ngăn Nhớ Và Tiến Trình Xử Lý Tại Tst -

Quá Trình Truyền Thông Tin Giữa Các Trạm Kết Cuối Trong Tcp/ip

Quá Trình Truyền Thông Tin Giữa Các Trạm Kết Cuối Trong Tcp/ip -

Sơ Đồ Khối Chức Năng Của Một Hệ Thống Chuyển Mạch Atm

Sơ Đồ Khối Chức Năng Của Một Hệ Thống Chuyển Mạch Atm

Xem toàn bộ 201 trang tài liệu này.

Hình 4.8 Sơ đồ khối chuyển mạch thời gian

Hình 4.8 chỉ ra sơ đồ nguyên lý cấu trúc của trường chuyển mạch thời gian T. Trường chuyển mạch thời gian T có hai kiểu điều khiển: Điều khiển đầu vào thực hiện quá trình ghi thông tin có điều khiển và đọc ra tuần tự; Điều khiển đầu ra thực hiện ghi thông tin tuần tự và đọc ra theo điều khiển. Trong mục này ta xem xét nguyên lý hoạt động của trường chuyển mạch T theo kiểu điều khiển đầu ra.

4.2.2.2 Cấu tạo

Trường chuyển mạch thời gian T được cấu tạo từ 2 khối chính: Khối bộ nhớ thoại SM (Speech Memory) và khối điều khiển cục bộ LOC.

Khối bộ nhớ thoại SM: là một thiết bị ghi nhớ truy xuất ngẫu nhiên RAM (Số lượng ngăn nhớ n, dung lượng ngăn nhớ 8 bit). Như vậy, bộ nhớ SM lưu toàn bộ thông

tin trong một khung tín hiệu PCM. Để đảm bảo tốc độ luồng thông tin qua trường

chuyển mạch, tốc độ ghi đọc của CM phải lớn gấp 2 lần tốc độ luồng trên tuyến PCM đầu vào hoặc đầu ra.

Khối điều khiển khu vực LOC: gồm một số khối như: Bộ nhớ điều khiển CM lưu trữ các thông tin điều khiển SM, số thứ tự của ngăn nhớ và nội dung dữ liệu trong CM thể hiện các chỉ số khe thời gian TS cần trao đổi nội dung tin. Counter nhận tín hiệu từ đồng hồ hệ thống để điều khiển các bộ chọn Selector1, Selector2 nhằm đồng bộ hoá quá trình ghi đọc thông tin dữ liệu cho CM và SM.

Số lượng ngăn nhớ của CM = số khe thời gian của luồng PCM = n. Dung lượng ngăn nhớ CM = Log2n.

PCM n×TS

TSi

n1 i 1 0

SM1

1

PCM I

0

i

n1

Add R/W

PCM n×TS

1

n1 j 1 0

TSj

LOC1

Add

Selector2

DEC

0

PCM O

Counter

R/W

Selector1

[ i ] j

n1

Clk W

CM1

Data

Hình 4.9 Nguyên lý chuyển mạch thời gian T điều khiển đầu ra

4.2.2.3 Nguyên lý hoạt động của chuyển mạch T điều khiển đầu ra

Nguyên tắc hoạt động của trường chuyển mạch thời gian T trên cơ sở

của

nguyên tắc trao đổi khe thời gian nội TSI. Hình 4.9 thể hiện kiểu điều khiển ghi vào tuần tự đọc ra có điều khiển SWRR (Sequence Write Random Read), để rõ hơn ta xem xét một ví dụ minh hoạ có yêu cầu chuyển đổi nội dung thông tin từ khe thời gian TS3 sang TS8.

* Quá trình ghi các thông tin:

Ghi thông tin thoại vào SM: Theo nguyên tắc ghi vào tuần tự, nội dung thông tin trong thoại trong TSi=TS3 sẽ được lưu vào ngăn nhớ i=3 (8bit).

Ghi thông tin điều khiển vào CM: Với yêu cầu chuyển đổi trên, hệ thống xử lý trung tâm sẽ chuyển thông tin tới CM thông qua đường dữ liệu điều khiển, bộ nhớ CM sẽ lưu chỉ số khe thời gian [i]="00011" dạng nhị phân vào ngăn nhớ j=8.

* Quá trình đọc thông tin:

Đọc thông tin điều khiển trong CM: Con trỏ địa chỉ của CM sẽ quét lần lượt, đồng bộ với các khe thời gian trên tuyến PCM, như vậy sau khi con trỏ địa chỉ trễ 5TS, nó trỏ đến ngăn nhớ j=8 trùng với thời điểm xuất hiện khe thời gian TSj=TS8 trong khung PCM. Bộ chọn Selector1 sẽ đọc nội dung trong ngăn nhớ j=8 của CM để yêu cầu đọc dữ liệu trong SM.

Đọc thông tin thoại trong SM: thông tin yêu cầu trong ngăn nhớ j=8 của CM được giải mã bởi DEC. Sau khi giải mã, tín hiệu yêu cầu đã giải mã được chuyển tới Bộ chọn Selector2 của SM nội dung là địa chỉ ngăn nhớ i=3 để yêu cầu Selector2 đưa con trỏ địa chỉ tới ngăn nhớ i=3, đồng thời cấp tín hiệu điều khiển đọc ra nội dung thông tin thoại (TS3) tại ngăn nhớ i=3 của SM.

Như vậy, tại thời điểm xuất hiện khe thời gian TS8, toàn bộ nội dung thông tin của TS3 được chuyển qua trường chuyển mạch. Quá trình chuyển mạch được lặp lại theo chu kỳ 125μs để hình thành nên kênh thông tin qua trường chuyển mạch.

Trong ví dụ trên khi i<j, chuyển mạch T gây trễ (ji)=5 TS, như vậy các TS nằm trong cùng một khung PCM, trường hợp kết nối TSi tới TSj với i>j thì không thể trễ âm

về thời gian được nên bắt buộc phải chờ đến khung tiếp theo. Ví dụ, kết nối TS8

PCM I tới TS3 PCM O. Quá trình ghi thông tin tương tự ví dụ trên. Thông tin thoại được ghi vào ngăn nhớ 8 của SM. Nội dung "00011" được ghi vào ngăn nhớ 3 của CM.

Quá trình đọc thông tin thoại được thực hiện tại thời điểm sau khi trễ đi (n+ji)

=32+38=27 TS. Khi đó bộ đếm đã quét hết các ngăn nhớ từ TSi = TS8 tới TSn1 = TS31 sau đó quay trở lại từ TS0 tới TSj = TS3 đúng lúc này thông tin thoại mới được đọc ra.

4.2.2.4 Nguyên lý chuyển mạch T điều khiển đầu vào

PCM n×TS

TSi

n1

i 1 0

PCM I1

Nếu cùng với yêu cầu chuyển mạch từ TS3 sang TS8 và trường chuyển mạch hoạt động theo kiểu ghi vào có điều khiển và đọc ra tuần tự RWSR (Random Write Sequence Read) thì tại ngăn nhớ i=3 của CM sẽ lưu thông tin địa chỉ [j]="01000". Cụ thể, hoạt động của chuyển mạch T điều khiển đầu vào như sau.

Add

SM1

0

R/W

LOC1

Selector2

DEC

Add 0

R/W

Selector1

[ j ]

i

n1

Clk

W

CM1

Data

Counter

j

n1

PCM O1

PCM n×TS

n1 j 1 0

TSj

Hình 4.10 Nguyên lý chuyển mạch thời gian T điều khiển đầu vào

* Quá trình ghi các thông tin:

Ghi thông tin điều khiển vào CM: căn cứ vào yêu cầu của cuộc gọi, dữ liệu điều khiển được hệ thống xử lý trung tâm ghi vào CM, ngăn nhớ i=3 của CM sẽ lưu chỉ số khe thời gian [j]="01000" dạng nhị phân là thời điểm cần đọc ra thông tin thoại. Thông tin yêu cầu trong ngăn nhớ i=3 của CM được giải mã bởi DEC.

Ghi thông tin thoại vào SM: Sau khi giải mã, tín hiệu yêu cầu đã giải mã được chuyển tới Bộ chọn Selector2 của SM nội dung là địa chỉ ngăn nhớ j=8 để yêu cầu Selector2 đưa con trỏ địa chỉ tới ngăn nhớ j=8, đồng thời cấp tín hiệu điều khiển ghi nội dung thông tin thoại (TS3) vào ngăn nhớ j=8 của SM. Theo nguyên tắc ghi vào có điều khiển, nội dung thông tin trong thoại trong TSi=TS3 sẽ được lưu vào ngăn nhớ j=8

(8bit).

* Quá trình đọc thông tin:

Đọc thông tin điều khiển trong CM: Con trỏ địa chỉ của CM sẽ quét lần lượt, đồng bộ với các khe thời gian trên tuyến PCM, quá trình đọc thông tin thoại trong CM được thực hiện một cách tuần tự. Như vậy, đến thời điểm TS3 nội dung ngăn nhớ i=3

được đọc. Thông tin thu được là địa chỉ

ngăn nhớ

[j]="01000", sau khi giải mã thu

được j=8 Bộ chọn Selector1 sẽ gửi yêu cầu tới Selector2 để yêu cầu đọc dữ liệu trong SM.

Đọc thông tin thoại trong SM: quá trình đọc thông tin thoại trong CM được thực hiện một cách tuần tự, đến thời điểm TS8 nội dung thông tin thoại tại ngăn nhớ j=8 ("TS3") của SM được đọc ra.

Như vậy, đã thực hiện được kết nối (với i<j) giữa TS3 tới TS8. Đối với kết nối có i>j các khe thời gian sẽ được phân bố trong 2 khung liên tiếp tương tự như trường hợp đã xét.

Trường chuyển mạch thời gian T mang tính không gian nếu xét trên khía cạnh vị trí thông tin dữ liệu trong các ngăn nhớ của CM. Chuyển mạch T luôn gây trễ tín hiệu và độ trễ lớn nhất không vượt quá một khung PCM, TDmax = (n1)TS. Do tốc độ ghi đọc của bộ nhớ yêu cầu lớn gấp 2 tốc độ luồng PCM nên số lượng khe thời gian trong một khung không vượt quá 1024 TS do giới hạn của công nghệ vật liệu điện tử. Để mở rộng dung lượng, người ta lựa chọn giải pháp ghép với các trường chuyển mạch không gian S.

4.2.3 Trường chuyển mạch mạch ghép

4.2.3.1 Khái quát

Trong các ứng dụng thực tế của các khối chuyển mạch tín hiệu số ta thường phải giải quyết hai vấn đề quan trọng là chất lượng dịch vụ QoS (Quality of Service) và dung lượng cần thiết của khối chuyển mạch yêu cầu. Chất lượng phục vụ chủ yếu phụ thuộc vào hiện tượng tắc nghẽn (blocking) và hiện tượng này với xác suất khá lớn khi chỉ sử dụng các chuyển mạch tầng S. Đối với tầng T như đã mô tả trên, nó có thể đảm bảo chức năng chuyển mạch không tắc nghẽn cho tất cả các khe thời gian trong luồng tín hiệu tốc độ cao PCM mà nó phục vụ.

Ví dụ với hệ thống 32 luồng PCM 30/32 được ghép kênh số thành một luồng cao tốc PCM 1024 TS hướng tới chuyển mạch tầng T đơn lẻ thì tất cả 1024 TS có thể được kết nối một cách tự do mà không gây hiện tượng tắc nghẽn. Nếu một trường chuyển mạch được xây dựng bằng một tầng T như vậy thì dung lượng thực tế của nó là 512 TS (1024/2) để thực hiện kết nối các kênh PCM theo cả hai chiều thu/phát. Tuy vậy, trong các ứng dụng thực tế ở tổng đài nội hạt, trường chuyển mạch ngoài việc tạo kênh cho kênh thoại còn phải tạo kênh cho báo hiệu và điều khiển. Do đó, với một tầng T đơn thì trường chuyển mạch chỉ bảo đảm được khoảng 450 thuê bao nghĩa là dung lượng tổng đài quá nhỏ.

Ngoài ra đối với công nghệ chế tạo khi kích thước tầng S tăng lên thì số lượng chân ra của vi mạch cũng sẽ rất lớn gây khó khăn chế tạo vi mạch. Còn việc tăng dung lượng của chuyển mạch tầng T thì phụ thuộc vào công nghệ chế tạo vi mạch nhớ RAM và các mạch logic điều khiển liên quan. Mục tiêu kết nối đa tầng chuyển mạch không chỉ nhằm tăng dung lượng hệ thống mà còn làm giảm bớt độ phức tạp và