[ s O ] = (H K

s 1

H) –1

Maybe you are interested!

-

Car body electrical practice - 8

zt2i3t4l5ee

zt2a3gs

zt2a3ge

zc2o3n4t5e6n7ts

If the voltage is out of specification, replace the wire or connector.

If the voltage is within specification, install the front fog light relay and follow step 5.

Step 5 Check the front fog light switch

- Remove the D4 connector of the fog light switch

- Use a multimeter to measure the resistance of the front fog light switch.

Measurement location

Condition

Standard

D4-3 (BFG) -D4-4 (LFG)

Light switchFront Fog OFF

>10kΩ

D4-3 (BFG) -D4-4 (LFG)

Front fog light switchON

<1 Ω

- Standard resistor

D4 connector is located on the combination switch assembly.

If the resistance is out of specification, replace the combination switch (the fog light switch is located in the combination switch).

If the resistance is within specification, follow step 6.

Step 6 Check wiring and connectors (front fog light relay-light selector switch)

- Disconnect connector D4 of the combination switch assembly

- Use a voltmeter to measure the voltage value of jack D4 on the wire side.

Measurement location

Control modecontrol

Standard

D4-3 (BFG) - (-) AQ

TAIL

11 to 14 V

D4 connector for the wiring of the combination switch assembly

If the voltage does not meet the standard, replace the wire or connector.

If the voltage is within standard, there may have been an error in the previous measurements.

Step 7 Check the front fog lights

- Remove the front fog light electrical connector.

- Supply battery voltage to the fog lamp terminals

Jack 8, B9 of front fog lamp on the electrical side

blind first.

Power supply location

Terms and Conditions

Battery positive terminal - Terminal 2Battery negative terminal - Terminal 1

Fog lightsbefore morning

- If the light does not come on, replace the bulb.

If the light is on, re-plug the jack and continue to step 8.

Step 8 Check wiring and connectors (relay and front fog lights)

- Disconnect the B8 and B9 connectors of the front fog lights.

- Use a voltmeter to measure voltage at the following locations:

Measurement location

Switch location

Terms and Conditions

B8-2 - (-) AQ

Electric lock ON TAIL size switchFog switch ON

11 to 14 V

B9-2 - (-) AQ

Electric lock ONTAIL size switch Fog switch ON

11 to 14 V

B8 and B9 connectors on the front fog lamp wiring side

Voltage is not up to standard, repair or replace the jack. If up to standard, there may have been an error in the measurement process.

2.2.4. Procedure for removing, installing and adjusting fog lights 1. Procedure for removing

- Remove the front inner ear pads

Use a screwdriver to remove the 3 screws and remove the front part of the front inner ear liner

-Remove the fog light assembly

+ Disconnect the connector.

+ Use a screwdriver to remove 3 screws to remove the fog light cover

2. Installation sequence

-Rotate the fog lamp bulb in the direction indicated by the arrow as shown in the figure and remove the fog lamp from the fog lamp assembly.

-Rotate the fog light bulb in the direction indicated by the arrow as shown in the figure and install the light into the fog light assembly.

- Use a screwdriver to install the fog light cover

-Install the electrical connector

Attention: Be careful not to damage the plastic thread on the lamp assembly.

- Install the front inner ear pads

Use a screwdriver to install the front inner bumper with 3 screws.

3. Prepare the vehicle to adjust the fog light convergence. Prepare the vehicle:

- Make sure there is no damage or deformation to the vehicle body around the fog lights.

- Add fuel to the fuel tank

- Add oil to standard level.

- Add engine coolant to standard level.

- Inflate the tire to standard pressure.

- Place spare tire, tools and jack in original design position

- Do not leave any load in the luggage compartment.

- Let a person weighing about 75 kg sit in the driver's seat.

4. Prepare to check the fog light convergence

a/ Prepare the vehicle status as follows:

- Place the car in a dark enough place to see the lines. The lines are the dividing line, below which the light from the fog lights can be seen but above which it cannot.

- Place the car perpendicular to the wall.

- Keep a distance of 7.62 m between the center of the fog lamp and the wall.

- Park the car on level ground.

- Press the car down a few times to stabilize the suspension.

Note: A distance of approximately 7.62 m is required between the vehicle (fog lamp center) and the wall to adjust the convergence correctly. If the distance of 7.62 m cannot be achieved, set the correct distance of 3 m to check and adjust the fog lamp convergence. (Since the target area varies with the distance, please follow the instructions as shown in the figure.)

b/ Prepare a piece of thick white paper about 2 m high and 4 m wide to use as a screen.

c/ Draw a vertical line through the center of the screen (line V).

d/ Set the screen as shown in the picture. Note:

- Keep the screen perpendicular to the ground.

- Align the V line on the screen with the center of the vehicle.

e/Draw the reference lines (H, V LH and V RH lines) on the screen as shown in the figure.HINT:

Mark the center of the fog lamp on the screen. If the center mark cannot be seen on the fog lamp, use the center of the fog lamp or the manufacturer's name mark on the fog lamp as the center mark.

H line (fog light height):

Draw a line across the screen so that it passes through the center mark. Line H should be at the same height as the center mark of the fog light bulb.

Line V LH, V RH (center mark position of left fog lamp LH and right fog lamp RH):

Draw two lines so that they intersect line H at the center marks.

5. Check the fog light convergence

a/ Cover the fog lamp or remove the connector of the other side fog lamp to prevent light from the unchecked fog lamp from affecting the fog lamp convergence test.

b/ Start the engine.

c/ Turn on the fog lights and make sure that the dividing line is outside the standard area as shown in the drawing.

6. Adjust the fog light convergence

Use a screwdriver to adjust the fog light to the standard area by turning the toe adjustment screw.

Note: If the screw is adjusted too far, loosen it and then tighten it again, so that the last rotation of the light adjustment screw is clockwise.

3. Self-study questions

1. Describe the operating principle of the lighting system with automatic headlight function

2. Describe the operating principle of the lighting system with the function of rotating headlights when turning

3. Draw diagram and connect lighting system on Hyundai Porter car

4. Draw diagram and connect lighting system on Honda Accord 1992

5. Draw the lighting circuit on a 1993 Toyota Lexus

LESSON 3 MAINTENANCE AND REPAIR OF SIGNAL SYSTEM

I. IMPLEMENTATION GOAL

After completing this lesson, students will be able to:

- Distinguish between types of signals on cars

- Correctly describe common symptoms and suspected areas causing damage.

- Connecting signal circuits ensures technical requirements

- Disassemble, install, check, maintain and repair the signal system to ensure technical requirements.

- Ensure safety in work and industrial hygiene

II. LESSON CONTENT

1. General description

The signal system equipped on cars aims to create signals to notify other vehicles participating in traffic about the vehicle's operating status such as: stopping, parking, braking, reversing, turning...

Signals are used either by light such as headlamps, brake lights, turn signals….. or by sound such as horns, reverse music….

Just like the lighting system. A signal system circuit usually consists of: battery, fuse, wire, relay, electrical load and control switch. Only some switches of the signal system are on the combination switch. The switches of other signals are usually located in different locations such as in the gearbox or brake pedal……

2. Maintenance and repair

2.1. Turn signals and hazard lights

The installation location of the turn signal is shown in Figure 3.1. The turn signal control switch is located in the combination switch under the steering wheel. Turning this switch to the right or left will make the turn signal turn right or left.

The hazard light switch is used when the vehicle has a problem while participating in traffic. When the hazard light switch is turned on, all the turn signals on the vehicle will light up at a certain frequency. The hazard light switch is usually placed separately from the turn signal switch (some old cars integrate the hazard and turn signal switches on the same combination switch cluster).

Figure 3.1 Turn signal switch Figure 3.2 Hazard switch

The part that generates the flashing frequency for the lights is called a turn signal relay. The turn signal relay usually has 3 terminals: B (positive power supply); E (negative power supply); L (providing the turn signal switch to distribute to the

lamp)

2.1.1. Circuit diagram

To generate the frequency for the turn signal, a turn signal relay is used in the turn signal circuit. The current from the turn signal relay will be sent to the turn signal switch assembly to distribute the current to the turn signal lights for the driver's purpose.

Figure 3.3. Schematic diagram of a turn signal circuit without a hazard switch

1. Battery; 2. Electric lock; 3. Turn signal relay; 4. Turn signal switch; 5. Turn signal lamp; 6. Turn signal lamp; 7. Hazard switch

Figure 3.4 Schematic diagram of turn signal circuit with hazard switch

1. Battery; 2. Combination switch cluster; 3. Turn signal;

4. Turn signal light; 5. Turn signal relay

Today's cars no longer use three-pin turn signal relays (B, L, E) but use eight-pin turn signal relays (figure 3.5) (pin number 8 is used for hazard lights).

For this type, the current supplying the turn signal lights is supplied directly from the turn signal relay to the lights.

div.maincontent .p { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; margin:0pt; } div.maincontent p { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; margin:0pt; } div.maincontent .s1 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; } div.maincontent .s2 { color: black; font-family:"Times New Roman", serif; font-style: italic; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s3 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s4 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; } div.maincontent .s5 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; vertical-align: 1pt; } div.maincontent .s6 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 11pt; } div.maincontent .s7 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; vertical-align: -9pt; } div.maincontent .s8 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 11pt; } div.maincontent .s9 { color: #008000; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s10 { color: black; font-family:"Times New Roman", serif; font-style: italic; font-weight: normal; te

Car body electrical practice - 8

zt2i3t4l5ee

zt2a3gs

zt2a3ge

zc2o3n4t5e6n7ts

If the voltage is out of specification, replace the wire or connector.

If the voltage is within specification, install the front fog light relay and follow step 5.

Step 5 Check the front fog light switch

- Remove the D4 connector of the fog light switch

- Use a multimeter to measure the resistance of the front fog light switch.

Measurement location

Condition

Standard

D4-3 (BFG) -D4-4 (LFG)

Light switchFront Fog OFF

>10kΩ

D4-3 (BFG) -D4-4 (LFG)

Front fog light switchON

<1 Ω

- Standard resistor

D4 connector is located on the combination switch assembly.

If the resistance is out of specification, replace the combination switch (the fog light switch is located in the combination switch).

If the resistance is within specification, follow step 6.

Step 6 Check wiring and connectors (front fog light relay-light selector switch)

- Disconnect connector D4 of the combination switch assembly

- Use a voltmeter to measure the voltage value of jack D4 on the wire side.

Measurement location

Control modecontrol

Standard

D4-3 (BFG) - (-) AQ

TAIL

11 to 14 V

D4 connector for the wiring of the combination switch assembly

If the voltage does not meet the standard, replace the wire or connector.

If the voltage is within standard, there may have been an error in the previous measurements.

Step 7 Check the front fog lights

- Remove the front fog light electrical connector.

- Supply battery voltage to the fog lamp terminals

Jack 8, B9 of front fog lamp on the electrical side

blind first.

Power supply location

Terms and Conditions

Battery positive terminal - Terminal 2Battery negative terminal - Terminal 1

Fog lightsbefore morning

- If the light does not come on, replace the bulb.

If the light is on, re-plug the jack and continue to step 8.

Step 8 Check wiring and connectors (relay and front fog lights)

- Disconnect the B8 and B9 connectors of the front fog lights.

- Use a voltmeter to measure voltage at the following locations:

Measurement location

Switch location

Terms and Conditions

B8-2 - (-) AQ

Electric lock ON TAIL size switchFog switch ON

11 to 14 V

B9-2 - (-) AQ

Electric lock ONTAIL size switch Fog switch ON

11 to 14 V

B8 and B9 connectors on the front fog lamp wiring side

Voltage is not up to standard, repair or replace the jack. If up to standard, there may have been an error in the measurement process.

2.2.4. Procedure for removing, installing and adjusting fog lights 1. Procedure for removing

- Remove the front inner ear pads

Use a screwdriver to remove the 3 screws and remove the front part of the front inner ear liner

-Remove the fog light assembly

+ Disconnect the connector.

+ Use a screwdriver to remove 3 screws to remove the fog light cover

2. Installation sequence

-Rotate the fog lamp bulb in the direction indicated by the arrow as shown in the figure and remove the fog lamp from the fog lamp assembly.

-Rotate the fog light bulb in the direction indicated by the arrow as shown in the figure and install the light into the fog light assembly.

- Use a screwdriver to install the fog light cover

-Install the electrical connector

Attention: Be careful not to damage the plastic thread on the lamp assembly.

- Install the front inner ear pads

Use a screwdriver to install the front inner bumper with 3 screws.

3. Prepare the vehicle to adjust the fog light convergence. Prepare the vehicle:

- Make sure there is no damage or deformation to the vehicle body around the fog lights.

- Add fuel to the fuel tank

- Add oil to standard level.

- Add engine coolant to standard level.

- Inflate the tire to standard pressure.

- Place spare tire, tools and jack in original design position

- Do not leave any load in the luggage compartment.

- Let a person weighing about 75 kg sit in the driver's seat.

4. Prepare to check the fog light convergence

a/ Prepare the vehicle status as follows:

- Place the car in a dark enough place to see the lines. The lines are the dividing line, below which the light from the fog lights can be seen but above which it cannot.

- Place the car perpendicular to the wall.

- Keep a distance of 7.62 m between the center of the fog lamp and the wall.

- Park the car on level ground.

- Press the car down a few times to stabilize the suspension.

Note: A distance of approximately 7.62 m is required between the vehicle (fog lamp center) and the wall to adjust the convergence correctly. If the distance of 7.62 m cannot be achieved, set the correct distance of 3 m to check and adjust the fog lamp convergence. (Since the target area varies with the distance, please follow the instructions as shown in the figure.)

b/ Prepare a piece of thick white paper about 2 m high and 4 m wide to use as a screen.

c/ Draw a vertical line through the center of the screen (line V).

d/ Set the screen as shown in the picture. Note:

- Keep the screen perpendicular to the ground.

- Align the V line on the screen with the center of the vehicle.

e/Draw the reference lines (H, V LH and V RH lines) on the screen as shown in the figure.HINT:

Mark the center of the fog lamp on the screen. If the center mark cannot be seen on the fog lamp, use the center of the fog lamp or the manufacturer's name mark on the fog lamp as the center mark.

H line (fog light height):

Draw a line across the screen so that it passes through the center mark. Line H should be at the same height as the center mark of the fog light bulb.

Line V LH, V RH (center mark position of left fog lamp LH and right fog lamp RH):

Draw two lines so that they intersect line H at the center marks.

5. Check the fog light convergence

a/ Cover the fog lamp or remove the connector of the other side fog lamp to prevent light from the unchecked fog lamp from affecting the fog lamp convergence test.

b/ Start the engine.

c/ Turn on the fog lights and make sure that the dividing line is outside the standard area as shown in the drawing.

6. Adjust the fog light convergence

Use a screwdriver to adjust the fog light to the standard area by turning the toe adjustment screw.

Note: If the screw is adjusted too far, loosen it and then tighten it again, so that the last rotation of the light adjustment screw is clockwise.

3. Self-study questions

1. Describe the operating principle of the lighting system with automatic headlight function

2. Describe the operating principle of the lighting system with the function of rotating headlights when turning

3. Draw diagram and connect lighting system on Hyundai Porter car

4. Draw diagram and connect lighting system on Honda Accord 1992

5. Draw the lighting circuit on a 1993 Toyota Lexus

LESSON 3 MAINTENANCE AND REPAIR OF SIGNAL SYSTEM

I. IMPLEMENTATION GOAL

After completing this lesson, students will be able to:

- Distinguish between types of signals on cars

- Correctly describe common symptoms and suspected areas causing damage.

- Connecting signal circuits ensures technical requirements

- Disassemble, install, check, maintain and repair the signal system to ensure technical requirements.

- Ensure safety in work and industrial hygiene

II. LESSON CONTENT

1. General description

The signal system equipped on cars aims to create signals to notify other vehicles participating in traffic about the vehicle's operating status such as: stopping, parking, braking, reversing, turning...

Signals are used either by light such as headlamps, brake lights, turn signals….. or by sound such as horns, reverse music….

Just like the lighting system. A signal system circuit usually consists of: battery, fuse, wire, relay, electrical load and control switch. Only some switches of the signal system are on the combination switch. The switches of other signals are usually located in different locations such as in the gearbox or brake pedal……

2. Maintenance and repair

2.1. Turn signals and hazard lights

The installation location of the turn signal is shown in Figure 3.1. The turn signal control switch is located in the combination switch under the steering wheel. Turning this switch to the right or left will make the turn signal turn right or left.

The hazard light switch is used when the vehicle has a problem while participating in traffic. When the hazard light switch is turned on, all the turn signals on the vehicle will light up at a certain frequency. The hazard light switch is usually placed separately from the turn signal switch (some old cars integrate the hazard and turn signal switches on the same combination switch cluster).

Figure 3.1 Turn signal switch Figure 3.2 Hazard switch

The part that generates the flashing frequency for the lights is called a turn signal relay. The turn signal relay usually has 3 terminals: B (positive power supply); E (negative power supply); L (providing the turn signal switch to distribute to the

lamp)

2.1.1. Circuit diagram

To generate the frequency for the turn signal, a turn signal relay is used in the turn signal circuit. The current from the turn signal relay will be sent to the turn signal switch assembly to distribute the current to the turn signal lights for the driver's purpose.

Figure 3.3. Schematic diagram of a turn signal circuit without a hazard switch

1. Battery; 2. Electric lock; 3. Turn signal relay; 4. Turn signal switch; 5. Turn signal lamp; 6. Turn signal lamp; 7. Hazard switch

Figure 3.4 Schematic diagram of turn signal circuit with hazard switch

1. Battery; 2. Combination switch cluster; 3. Turn signal;

4. Turn signal light; 5. Turn signal relay

Today's cars no longer use three-pin turn signal relays (B, L, E) but use eight-pin turn signal relays (figure 3.5) (pin number 8 is used for hazard lights).

For this type, the current supplying the turn signal lights is supplied directly from the turn signal relay to the lights.

div.maincontent .p { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; margin:0pt; } div.maincontent p { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; margin:0pt; } div.maincontent .s1 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; } div.maincontent .s2 { color: black; font-family:"Times New Roman", serif; font-style: italic; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s3 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s4 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; } div.maincontent .s5 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 13pt; vertical-align: 1pt; } div.maincontent .s6 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 11pt; } div.maincontent .s7 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; vertical-align: -9pt; } div.maincontent .s8 { color: black; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 11pt; } div.maincontent .s9 { color: #008000; font-family:"Times New Roman", serif; font-style: normal; font-weight: normal; text-decoration: none; font-size: 14pt; } div.maincontent .s10 { color: black; font-family:"Times New Roman", serif; font-style: italic; font-weight: normal; te -

Effect of Initial Glyphosate Concentration on Processability of Electrochemical Fenton Process

Effect of Initial Glyphosate Concentration on Processability of Electrochemical Fenton Process -

Cultivation and Production Process of Special Rare Weasel Coffee

Cultivation and Production Process of Special Rare Weasel Coffee -

Complete the retail process of kitchen utensils at Website Hanoi.Golmart.vn - 9

Complete the retail process of kitchen utensils at Website Hanoi.Golmart.vn - 9 -

Design and construction of color TV PAN model - 2

Design and construction of color TV PAN model - 2

y 11 y 12

y

H K [ ∗ ] ( 2.18)

21

y 22 ∗

After being processed, the signal will be fed into MLD (maximum likelihood decoder) to determine the original signal. Thanks to that, we will get the original signal.

2.2 Design tools.

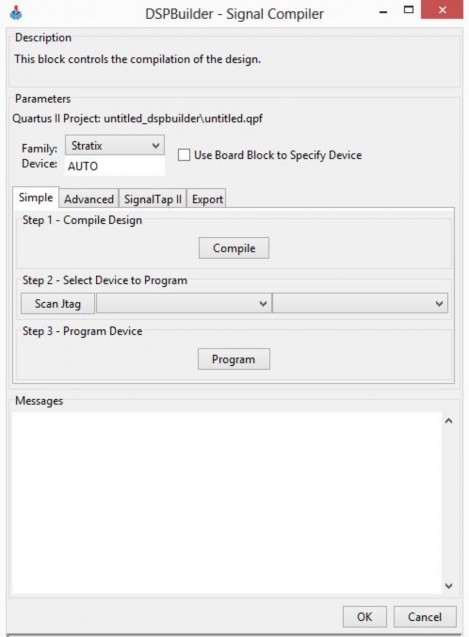

2.2.1 DSP Builder software.

The topic is designed using DSP Builder software, a utility designed by Altera to support users to quickly design digital signal processing applications. DSP Builder runs on Matlab's Simulink platform and inherits Simulink's simulation capabilities. Therefore, to use DSP Builder, users need to know about Matlab and Simulink first.

DSP Builder creates a friendly working environment for designing DSP systems. Thanks to the available function blocks, the design becomes easier. Users can create the desired applications and simulate on Simulink to check the results.

DSP Builder provides a tool to convert designs into VHDL format that allows compilation and synthesis into hardware configurations, helping to shorten the time it takes to turn ideas into reality.

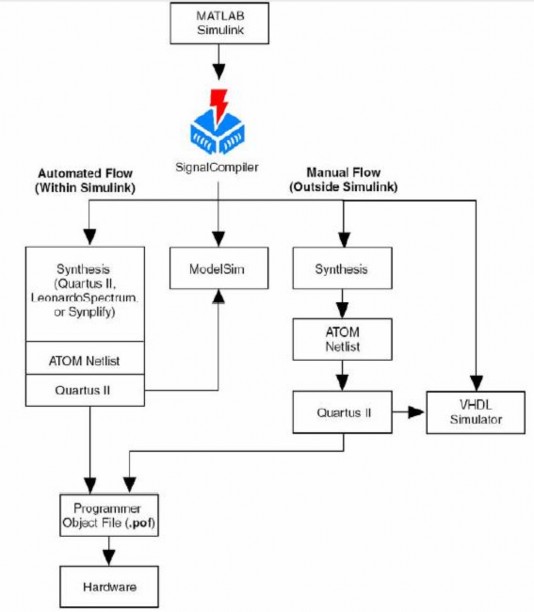

DSP Builder is characterized by its bit- and cycle-precision blocks that perform arithmetic and storage functions. They can integrate complex functions by using MegaCore Functions in the DSP Builder model. These Functions enhance the power of DSP Builder and open up a wide range of development possibilities. Error! Reference source not found. presents compilation methods to translate from schematic design to hardware.

Figure 2.10. DSP Builder design process

Matlab Simulink creates a model, using a combination of DSP Builder blocks and Simulink blocks.

RTL (Register Transfer Level) simulation representation: DSP Builder supports simulation for ModelSim software using Tcl scripts. VHDL generated can be used for simulation with other tools.

Use files generated by DSP Builder SignalCompiler block to synthesize RTL. DSP Builder supports Tcl scripts for automatic synthesis using other software programs such as: Quartus II, Synplify, Leonardo Spectrum.

In this thesis, design compilation is performed using Quartus II software version 13.1 and must be on Windows 64 bit platform.

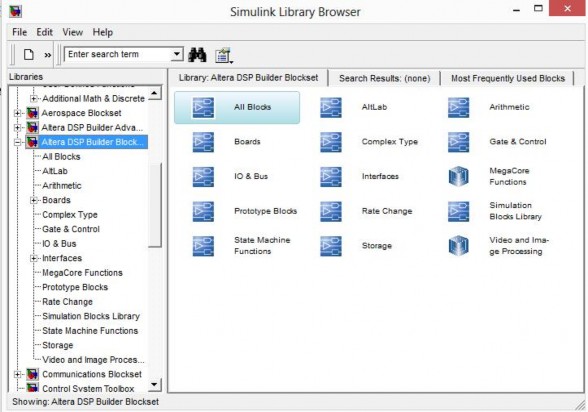

2.2.2 DSP Builder Library.

Figure 2.11. DSP Builder library

Figure 2.11 shows the library groups of DSP Builder. Depending on different versions, DSP Builder will have different libraries. But in general, the library includes the following basic functional blocks:

AltLab Library: This is a library containing design support blocks such as: block for selecting programming component type, block for importing a VHDL or Verilog HDL design into a subsystem, block for returning information: sampling period, maximum number of bits needed during simulation and maximum or minimum value received during simulation. There are two important blocks in the library: SignalCompiler block and SignalTap II Analysis block:

Figure 2.12. Signal Compiler block operation.

The Signal Compiler block is the most important block in DSP Builder. Figure 2.12 shows the interface when running Signal Compiler. This block has the following functions:

Convert Simulink design to RTL VHDL language Generate test files in VHDL or Verilog language

Generate Tcl scripts for Quartus II compilation, or for other software such as: Synplify, Precision RTL, LeonardoSpectrum TM and ModelSim.

Allows creation of SignalTap II (.stp) files

Create files using the Quartus II block format (.bsf)

The SignalTap II Analysis block is used to examine the signals inside the components while the system is running. SignalTap II Analysis can be used for triggers, memory configuration, and waveform display. This project uses this tool to examine each functional block and the data processing of the entire system.

Arithmetic Library: Library of blocks used for arithmetic operations such as comparison, differentiation, integration, multiplication, addition, square root, etc.

Board Library: The board used in the project is the Antenna Board. When we want to connect to any hardware of the board, we just need to add the blocks in the library to the design model.

Complex Type Library: The library provides functions related to complex numbers such as: adding and subtracting complex numbers, calculating amplitude, phase...

Gate and Control Library: This is a library that provides blocks for controlling data paths and logic gates such as multiplexers, demultiplexers, flip flops, AND gates, OR gates, invertors, etc.

IO and Bus Library: This library provides input/output and bus blocks such as: bus conversion (for example, converting from 20-bit bus to 16-bit bus, removing 4 bits), bit separation, source, mass, constants...

Rate Change Library: This library provides blocks to change the speed in the model, mainly used when we want to design a program with more than 1 clock.

The most important block in this library is the PLL block, and this block can only be used when placed at the top level of the model. Also, blocks that use the results of the PLL must be subsystems and not at the same level as the PLL.

Storage Library: The Storage Library provides memory blocks such as ROM, FIFO, LUT (look-up table: storing data in a look-up table)…

MegaCore Functions Library: MegaCore Functions are blocks that perform a complete function on their own, but DSP Builder does not provide these MegaCore Functions out of the box. These MegaCore Functions can be added and are often very complex to control.

2.3 Hardware implementation.

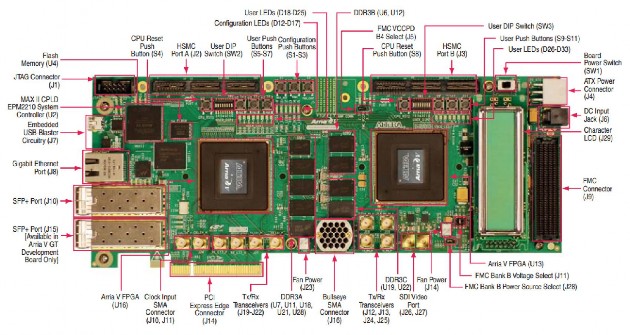

2.3.1 Arria V GT board introduction

Figure 2.13. Antenna Board.

Figure 2.13 is the Altera Arria V GT Development Kit. This kit provides a complete design environment, including all the hardware and software the user needs to develop all FPGA designs and test them in a system environment. The kit is RoHS compliant and includes the following features:

The two FPGAs for the system-level design are the Arria V GT: 504,000 logic elements (LEs), F1517 package, for transfer rates up to 10.3125 Gb/s.

Three input/output slots: 2 high-speed HSMC slots and 1 FMC slot

DDR3 SDRAM with 2Gb memory, QDR II+ with 4.5Mb memory and 1Gb flash memory.

Two SFP+ connections

High speed SMAs and Samtec Bull's Eye connections. Individual power measurements per chip possible.

2.3.2 Components on the Arria V GT board.

2.3.2.1 Antenna Device 5AGTFD7K3F40I3N

On the board there are 2 important devices: FPGA1 and FPGA 2 Arria V GT family with 1517 FineLine BGA pins

504000 logic elements (LEs)

190240 logic response modules (ALMs) M10K memory is 24140 Kb

MLAB memory is 2906 Kb 36 transceivers

16 phase-locked loops (PLLs) 2312 channels 18x18.

Internal voltage 1.15 V

FPGA 1 connects to the following components: Communication ports:

One 8-way PCI Express connection. One USB 2.0 connection

C2C bridge with 29 LVDS inputs, 29 LVDS outputs and 8 transmit and receive channels.

Two SFP+ channels

One 10 Gb/s SMA transmit and receive channel

Three 10 Gb/s Bull's Eye transmit and receive channels Memory:

DDR3 SDRAM 1152 Mb with 72 bit data bus. QDRII + SRAM 72Mb.

Flash synchronized with 16-bit data bus.

Import/export:

LED and LCD:

Eight red and blue 2-color LEDs. Two-line LCD.

Three LEDs indicate configuration selection One LED indicates configuration complete.

Two LEDs indicate HSMC transmit/receive. Three LEDs indicate PCI Express. Five LEDs indicate Ethernet.

Push button:

One push button resets the CPU.

One push button configuration control for MAX II

One push button to load the image into the FPGA from flash memory. One push button to select the image to load from flash memory.

Three push buttons for common use. Eight control switches.

The connection diagram of Arria V GT with the components on the board is as follows: